样品DDR400部分,样品 20PCS,有2PC 不能工作,不知是否与LAYOUT相关?

6层板,L1-signal 1,L2-GND,L3-signal 2, L4-signal 3, L5-Power, L6-signal 4,

DDR 数据、时钟线在L1和L3,部分地址线在L6,信号阻抗和差分线阻抗=50 OHM。

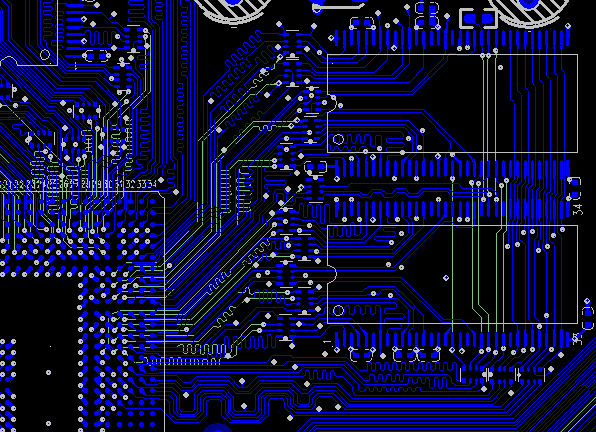

Top and Layer 3

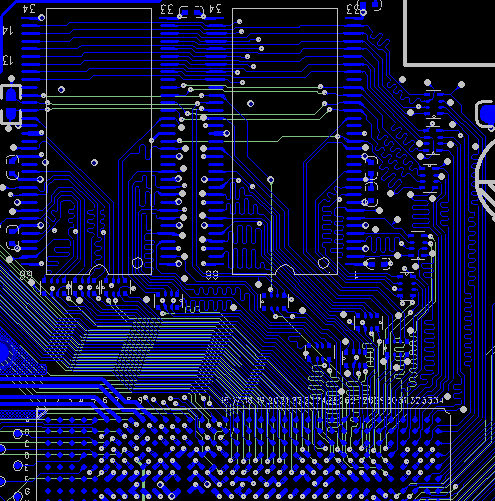

Top and Layer 3

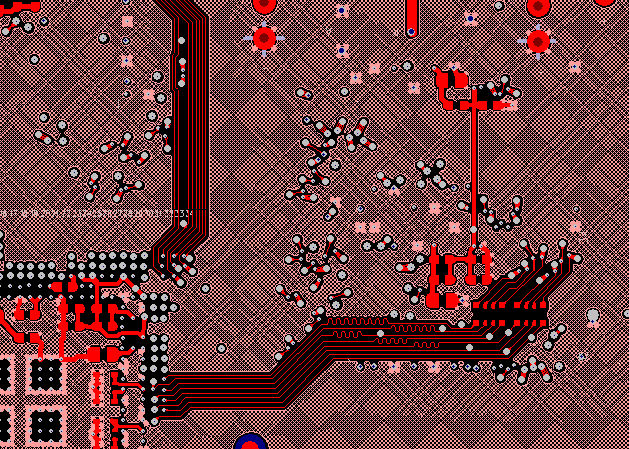

Bottom layer

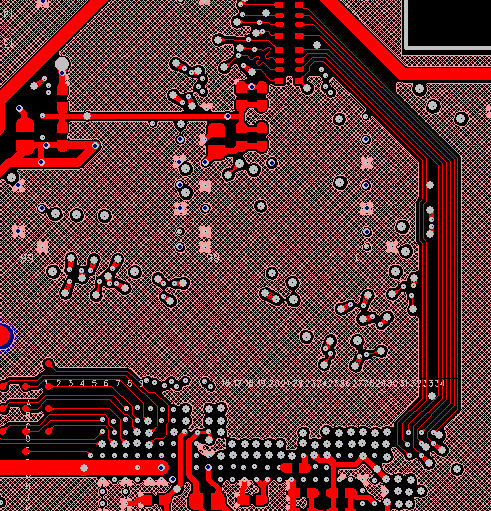

Bottom layer

有时间,简单说两句

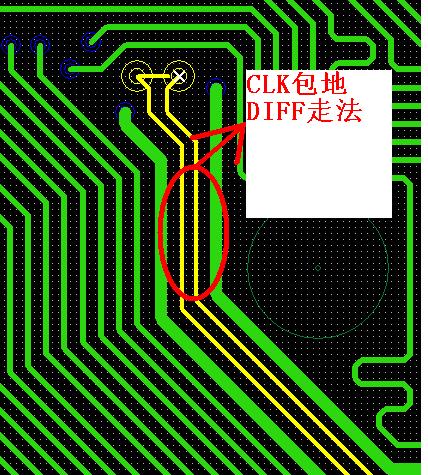

1.CLK是任何系统的关键,一般我们用两种处理方法,一种是3W规则,一种是包地,因为大部分空间限制,多数采用3W。

2.DQS、DQM这两根讯号应该走diff对

3.同组讯号应该走在同一层,不应跨层跨区

4.地址总线部分应该粗一些,如果数据线走5mil ,建议地址总线走8mil

5.建议所有走线用2W原则。

6.所有SDRAM部分讯号不要跨区。建议走到TOP和BOTTOM层,最好不走内层。

首先多谢大师“网上邻居”的指教,以下是我的另外一点看法和理解:

网上邻居:

1.CLK是任何系统的关键,一般我们用两种处理方法,一种是3W规则,一种是包地,因为大部分空间限制,多数采用3W。

2.DQS、DQM这两根讯号应该走diff对

3.同组讯号应该走在同一层,不应跨层跨区

4.地址总线部分应该粗一些,如果数据线走5mil ,建议地址总线走8mil

5.建议所有走线用2W原则。

6.所有SDRAM部分讯号不要跨区。建议走到TOP和BOTTOM层,最好不走内层。

讨论:

1. 3W、2W已考虑,比较你的图好象我的理解不对:2W=两线中心距为2W?(/3W?)

2. 总线等长考虑:地址总线CPU到RAM1等长, CPU到RAM2等长;还是CPU到RAM1 与CPU到RAM2都等长?

3. 没跨区,有跨层,但考虑VIA长度补偿,如30mil/VIA.

4. 差分线已考虑,另使用了5mil总线走线,但你说“如果数据线走5mil ,建议地址总线走8mil”,不知是考虑什么因素?

5. 另,看别人的LAYOUT,同样信号、网络如果跨层时,线宽会不同,如TOP 6mil, 内层4.8mil, 不知是否考虑叠层或其它方面的因素?

top 6mil,内层4.8mil主要是为了阻抗匹配,如50欧。

1)2W,3W本来应该是两线中心距,但看图片成了2线边缘的间距

4)不知道为什么地址线为什么要比数据线宽,有理由吗?

多谢tanye001、zzouyong!另外关于拓扑结构等长考虑:

2. 总线等长考虑:地址总线CPU到RAM1等长, CPU到RAM2等长;还是CPU到RAM1 与CPU到RAM2都等长?

我认为:总线CPU到SDRAM1等长, 总线CPU到SDRAM2等长,即分别等长。不知对否?

我不太明白为什么采用菊花链还能保证CPU到各SDRAM等长?请大师们指点!

看了图片小编的板子的DDR已经做了等长,时序上应该没有问题.但不知道同组8 位信号以及DQS,DQM是不是布在同一层而且靠一起布线,否则如果有干扰可能会产生误码.还有就是电源的完整性方面是否处理好了,DDR对电源要求是比较高的特别是VTT.还有如果时钟采用包地处理是否能保证阻抗的匹配.

谢谢Design_sophia!

1、同组8 位信号以及DQS,DQM是不是布在同一层而且靠一起布线,否则如果有干扰可能会产生误码.

同组信号部分是布在同一层而且靠一起布线,部分不是。全部运用此规则可能难布通。不知是否因此产生误码.另DQS,DQM差分线到SDRAM1,换层到SDRAM2,这里换层不知是否有影响?另外有些信号引线加测试点,不知是否有影响?

2、电源的完整性方面有考虑,不知是否处理全面。VREF、去耦、电源与地无跨区,还有其它?希望大家指点!

1. 地址信号的串联电阻,尽可能靠近CPU附近放置。

2. DQM和DQS不是差分信号,无需按照差分布线,最关键的是注意每8位数据+1 DQS+1DQM需要严格等长;

3. 走在背面的地址信号,因为参考平面不同,最好能换到L3,如果不行,最基本保证相邻的电源平面无分割,然后在地址信号过孔附近就近放置一些0.1uF的旁路电容

4. 信号之间间距尽可能拉大,绕线最好不要绕小弯角。

5. 可能的话,信号走线走“T”结构,菊花链不是最好。尤其是时钟信号,这里也是串联的,采用T才能保证时序上skew最小

6. Vref信号,最好不要走背面,因为相邻的是电源,走到靠近GND参考层,另外在管脚旁边放置去藕电容。

专业的就是不同,解释的很到位~~

赞一个~

多谢 PCBTECH总小编 的指正!

因样品在国外测试,我只是猜测是否与LAYOUT相关。多谢各位关注与指教!

信号走线走“T”结构好吗,不一定吧,两个分插很长的时候,“T”拓扑信号容易畸变,而小编的情况无法保证两个分插很短。菊花链仅仅增加延时,星型拓扑最好,但是很难走通

可以降低频率试下,看还能不能用。

顶,这样的贴子不顶不行,大侠们继续,偶关注中

那么多种说法,我晕