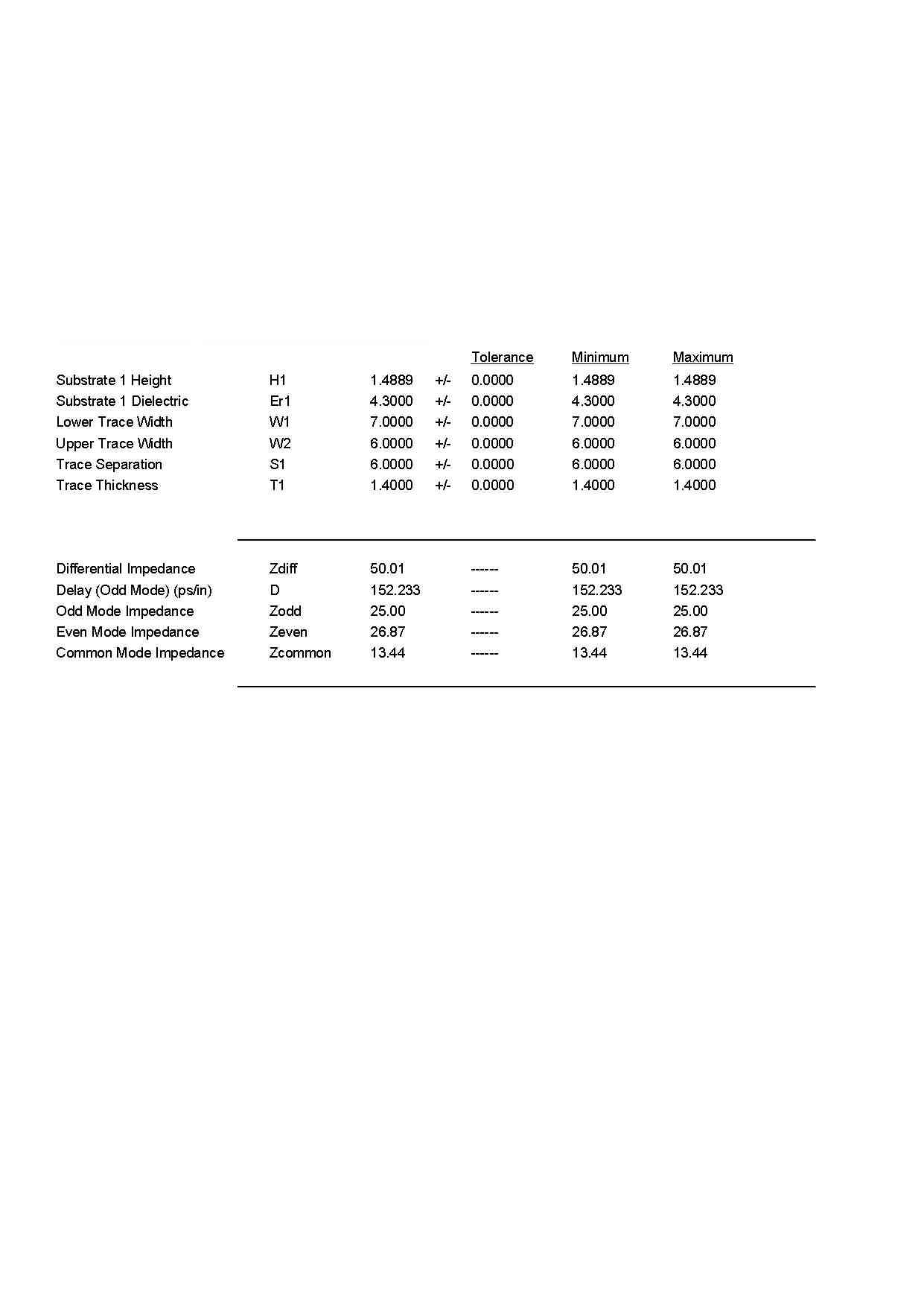

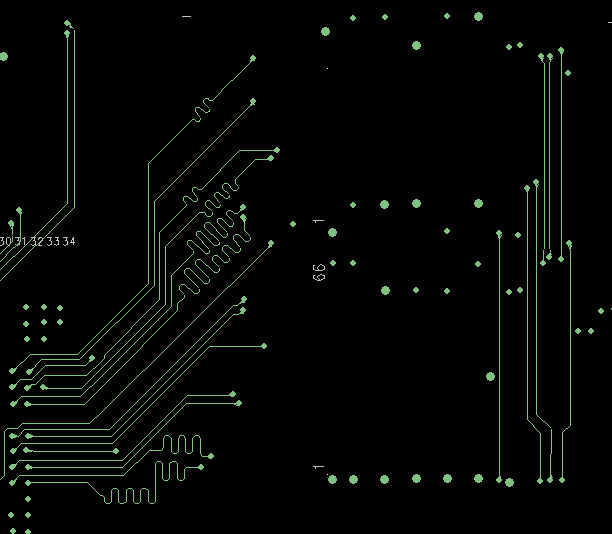

这样的layout能跑DDR 400M?

DDR

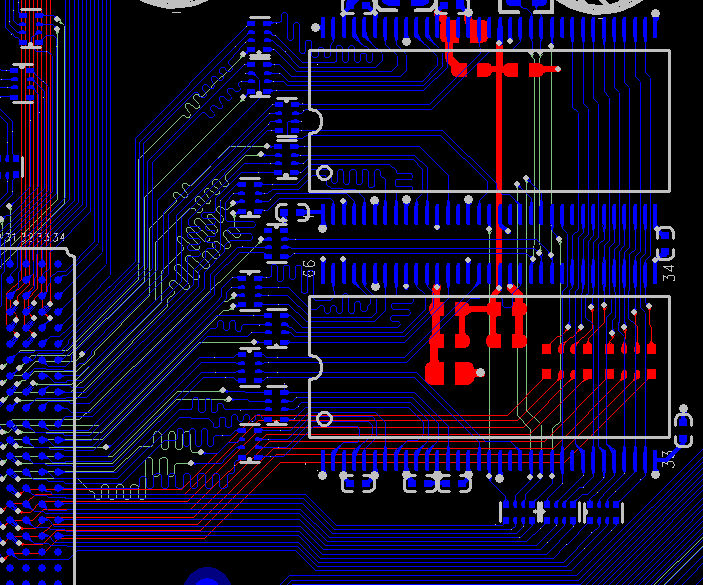

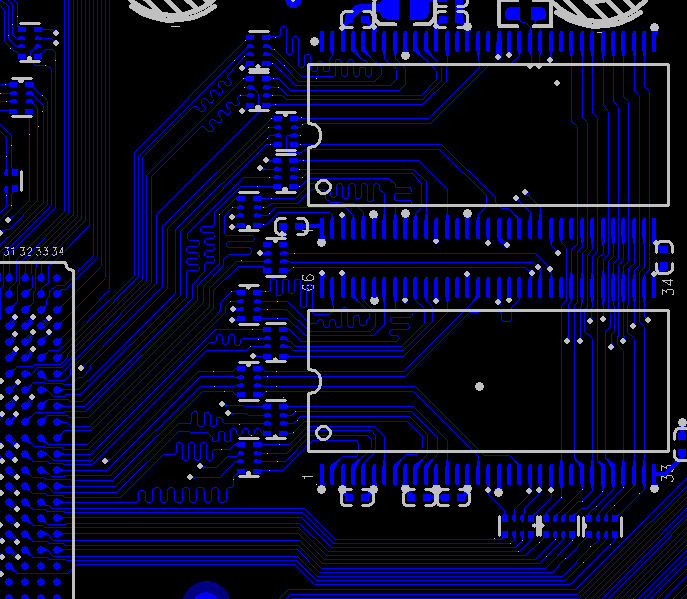

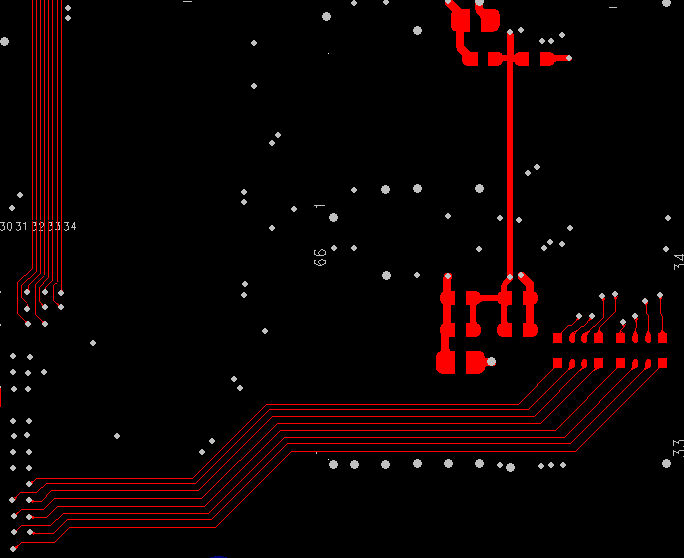

All group DQ, DQS <1600mil, CLK=1650mil, DQ, DQS CLK route on top and L3, signal AD on Top and Bottom.

Stack up Layers,

All layer

top

Bot

Layer 3

ddr2 没有这种封装的芯片吧

ddr1吧

以前也 跑过ddr 的板子,要求是线距是线宽的4倍(此一定要做到),其它沒有什麽要求。

非常多谢chensir 的指点;

di地址线做的不好,是否有考虑等长,到两颗DRAM的长度是否一样或差不多?

是的,漏了AD等长,另走线是菊花拓扑。另外看一下设计参考样品,它的相差更大。不知为什么?

是否有信号线跨层,内外层的阻抗是否做的一样?

有,要求PCB做阻抗控制,不知能否实现。

是DDR,写错了。多谢各位指教。

仅CK,DQS用3W,其它用2W规则。

如果用时序来考虑走线长度,在SPC中应选用哪个参数呢?

SPC是什么

sop封装的应该是DDR1, 用DDR1跑到400MHz,算是超频了,真不错唉...

设计参考样品,它的相差更大。不知为什么?

设计参考样品有算GPU的封装长度.

做主板,显卡的兄弟门都疯了.同一类型的地址数据线分这么开作甚?

400M的不需要严格等长,差不多就可以了

我的板子连50欧姆阻抗都没有做也照样运行如飞