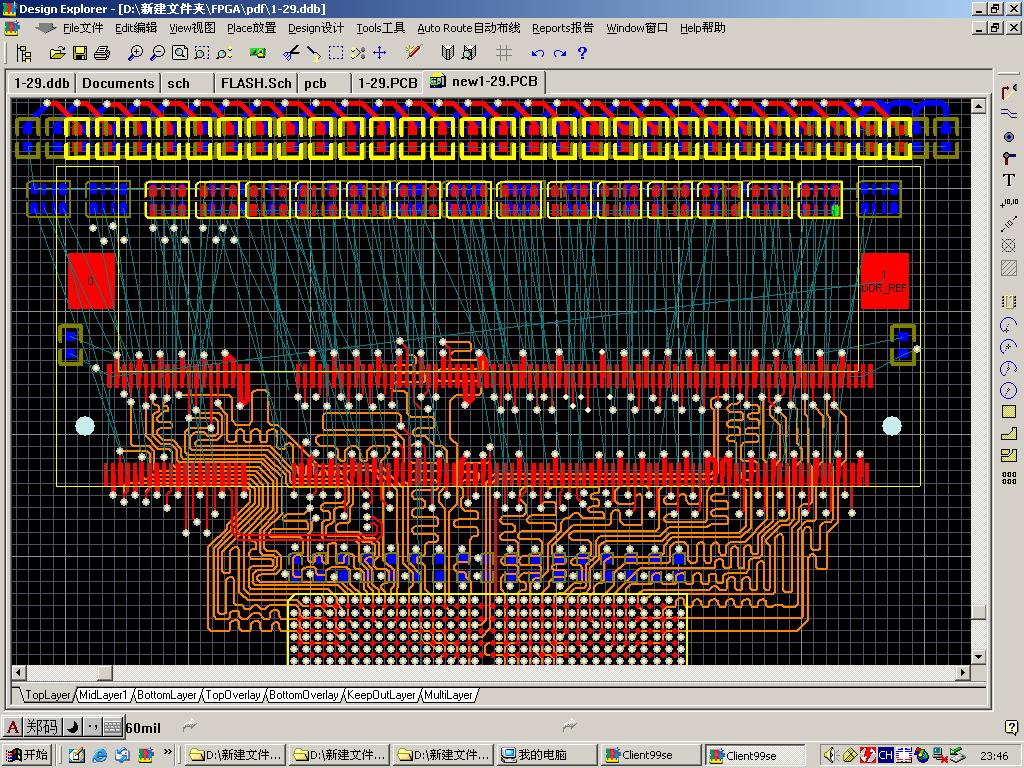

fpga与ddr部分更新,请大家指导

本人是第一次画,而且是ddr400,不敢大意,多方求教,经过大家们的指点,现在基本如图所示:

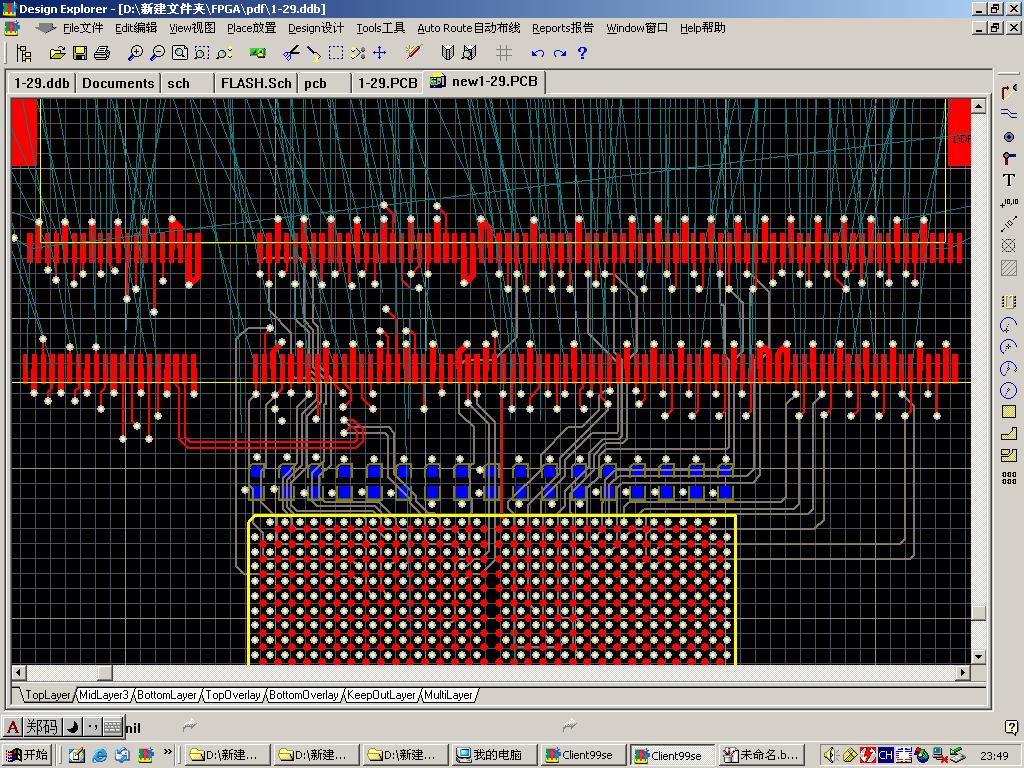

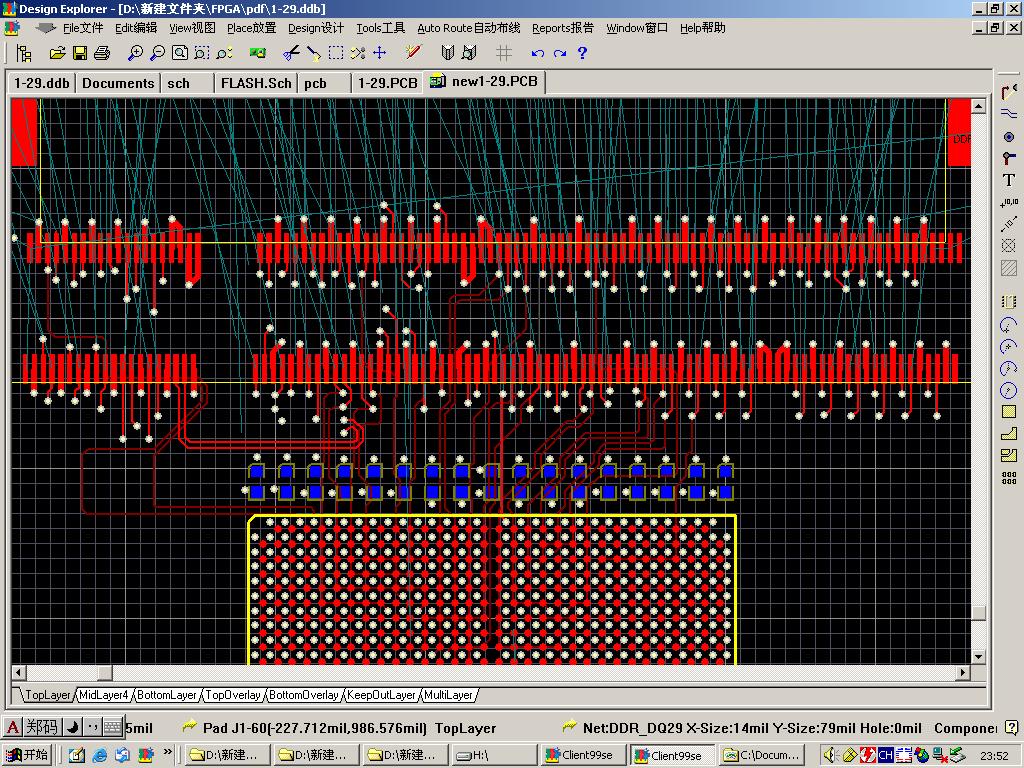

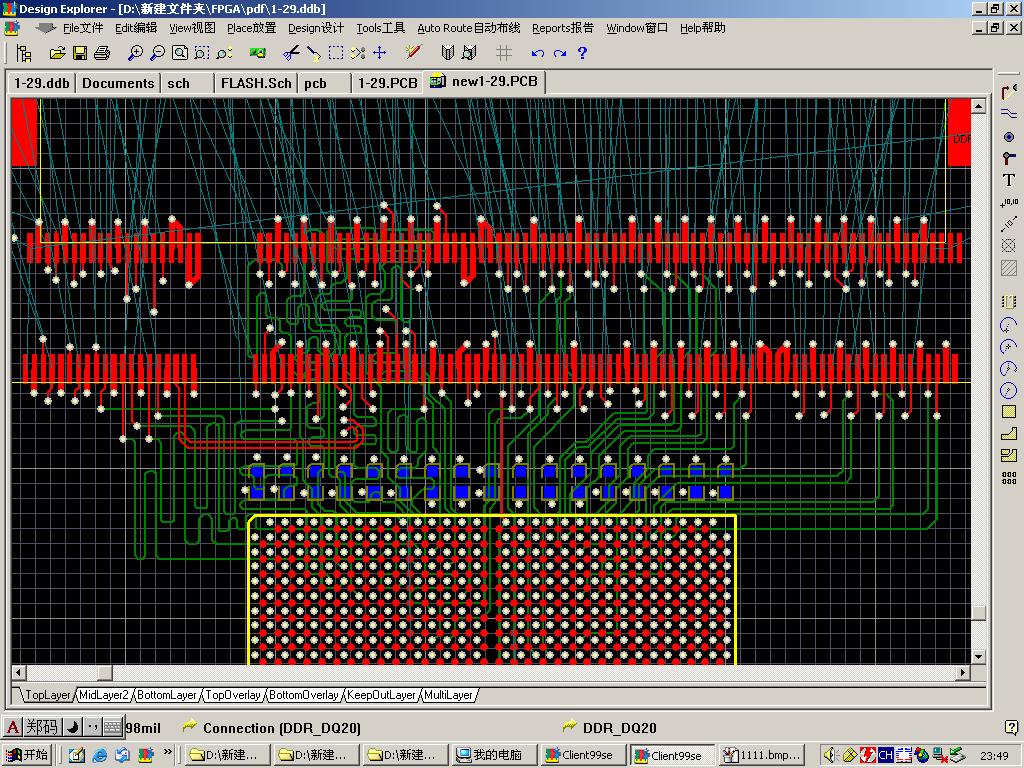

1:从fpga到串接电阻,dq,dqs以及dm统一通过两个过孔并绕等长,从串接电阻到ddr device,统一走底层和顶层。2:地址线与控制线采用T型拓扑,每根线3个过孔,从fpga到第一个过孔(就是中间斜着的那两列),准备绕等长;从第一个过孔到ddr device管脚,也都绕了等长,这样保证了地址线和控制线等长。其实如果有地方的话,那么地址线的过孔可以在中间竖直来打,这样左右两边就不用各自再绕了。3:fpga外圈那一排电阻是留给fpga的去藕电容等,现在暂时没用。

现在的问题是:

1:dq,dqs以及dm的长度都控制在1700mil,而地址线和控制线绕下来要到3500mil,这个差距会不会有些太大?但好像这个问题无法解决,因为地址线本身就在ddr和fpga的两头。

2:大家也看到了,从地址线的第一个过孔到ddr device,其实有些线,就是靠近地址线过孔的那些管脚,可以直接相连,但我都是通过芯片中间的那些过孔来分,这样做的目的主要是考虑到等长好绕,另外每根线的过孔数量也匹配,这种做法对么?

3:数据线也是一样的,对于fpga最外面两排的管脚,完全可以利用顶层直接和串接电阻相连,或者通过一个via利用底层和串接电阻相连,但我还都是统一采用了两个via这种方法,具体原因和地址线的考虑是一样的。

4:如果本着via尽量少的原则,那么绕等长的时候,是不是必须考虑via带来的等效长度,按照一位高手的说法,一个via=40mil?

5:时钟线还没有走,4片时钟线连接在一起,那么不可能只有两个过孔,应该起码也像地址线那样,有三个过孔了,不知道大家有什么好办法,可不可以在fpga中分开接,然后用内部pll实现几个时钟同相位?

谢谢大家

我觉得应从各信号的时序考虑入手会好些

我没有布过这样的板,具体问题还得具体对待。

我想应是数据线组等长,地址线组等长,数据线或地址线与时钟线或其他的

控制线就得满足时序关系要求了。这是根本问题。

不过还是希望大家热情讨论。

关注中。

其实,这次用的fpga提供ddr的专用管脚(altera还有好几种都提供),对于管脚顺序,也就是组内的8根可以调整,像dqs,dm都是固定管脚,我感觉对于这种经典摆放方式,altera应该提供一个标准的布线参考(主要是管脚安排和出线方式最重要,当然最好还有ddr device与fpga之间的距离,两片ddr device的距离等),以免大家走弯路,这次我就是摸索了很多种方案,才定下来目前这种,个人感觉应该是比较合理的。

听说xillinx就提供fpga与ddr接口的参考布局,但没有用过,不知道到底如何。

谢谢大家

我认为布这部分电路的顺序应该先考虑时钟线,而且大部分时钟信号要求差分走线,然后是数据线,其次DQ,DQS,DQM(这三种信号线是与着数据线匹配的),然后才是地址线,(匹配线长误差满足芯片DATASHEET)。

我有6个信号层,因此时钟线还是有地方走的,地址线您讲到的匹配长度?请问是地址线之间的匹配呢?还是地址线与数据线之间的匹配?谢谢大家

高手们看一下啊,现在对于地址线和数据线差距那么大,感觉心里很不踏实啊,另外我的时钟线的长度也要比dq长一点

這種我也沒布過,我認為,clk不論走在那一層,他的參考電源層都應該是gnd;

地址線我認為並沒有規定過孔數量匹配,所以有些via可以省掉;

數據線每一組應走在同層,所以若你一組的bus走頂層走不出來的話,應該就要打via廖.

對於地址,數據,和clk線三者之間等長問題,只要滿足時序,差很多也是正常的.

這只是個人經驗.

知道这里画过ddr slot的人不少,还请看看

这个东西没有意义么?

好贴,我收藏了

关注中,请小编继续分析啊!