GND 切割

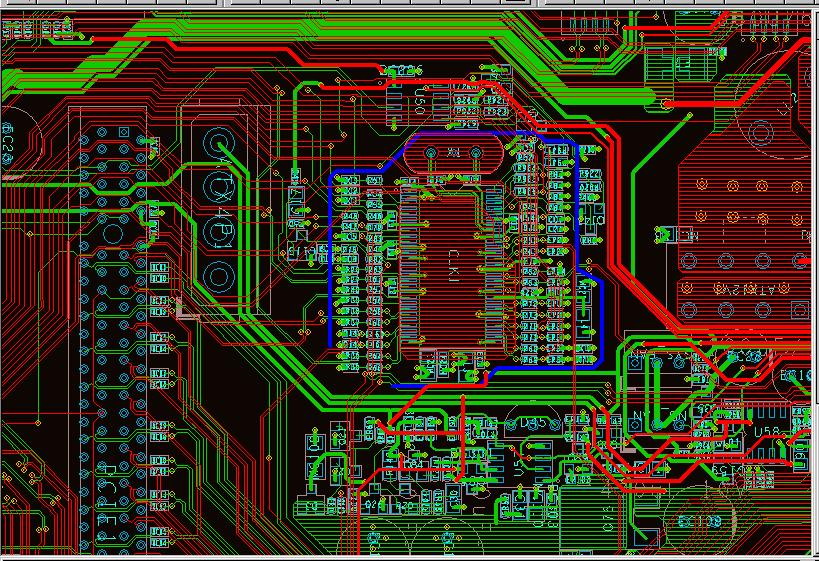

有谁见过这种GND切割方式?本来只是I/O单独切一块GND,其他的地方是一块GND。但是现在 在时钟芯片下方的GND切割出来一小块GND,这样切有什么好处?

这个地方是模拟电路,当然要和数字电路分开。

这里是数字信号...

沒有人能幫忙解答嗎?

没有看到图片啊

可以啊,直接就能看到...

你刷新一下看看

没人响应,自己ding

没见过这样分割的,只是有把CLK电路做局部地的,就是在元件层把CRYSTAL下方铺上地,和CRYSTAL外壳接触,但是地层没见过分割的。

这样的没见过,出去的信号岂不要垮分割了?

就是因为会存在这样的问题(跨线),所以我才来问一下的...

有没有办法帮忙解答一下,这种切割还是存在的。

高手,期待ing...

同意,局部做地,没有见过在地层单独做地的,否则clk怎么满足loop gain和phrase的要求,

这样做应该不符合现在的理论,但是在过去使用这些方法还是很多的。主要的原因是,跨分割是会对EMI有负面的影响,但是由于各个电路的抗干扰能力不同,不一定产生致命影响。在过去,时钟电路,尤其是Cystal,会在地上产生很大噪声,这些噪声的影响比较大。但是这些噪声在离开中心1CM的地方测试,幅度会下降非常多。所以大家的做法就是在Crystal下铺铜皮,将Crystal的外壳焊在铜皮上,再连接到(有时会将Crystal下的地挖掉),然后将地分割,让开口的方向在晶振的对角方向,而且要保证开口的方向是对着比较开阔的方向,让地噪声有足够空间降低。

过去设计人员没有重视电路的速度,对电路的速度也相对于现在是低的,没有成为主要问题。现在,主频不断提高,3。3V电路,甚至更低电压的电路在使用,不能在忽视跨分割的EMI问题。

Top layer: signal layer,

second layer:Power layer,

Third layer: Ground layer,

Bottom layer:Signal layer。

Moat at Ground layer(third layer)。

Thanks...

太厲害了﹐以前的設計也這么清楚

頂上去,期待更多答復...

是不是防止CRYSTAL的噪声在地层上的扩散阿?

偶是新手,随便说说!

减小寄生电容

呵呵,有意思!

我来单位就发现我们的PLL电路全是这么搞的……

我无语……

领导嘱咐:其他地方你都可以动,这里,别动……

唉!

昨天,服务器的大底版终于出现SI的问题了,高兴,该重视了吧?……

学习中...

chenylcyzg,

你们服务器的大底版终于出现SI的问题了

具体是什么现象呢,呵呵