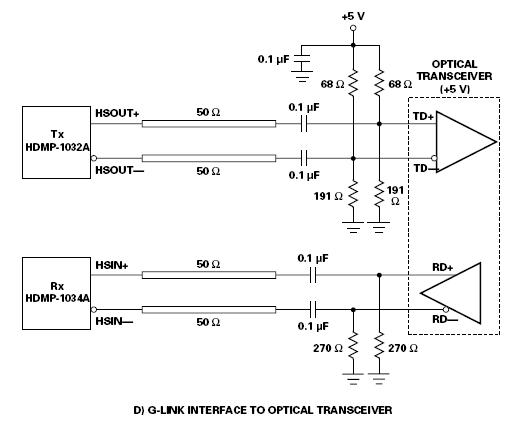

1G的差分信号如何布线?

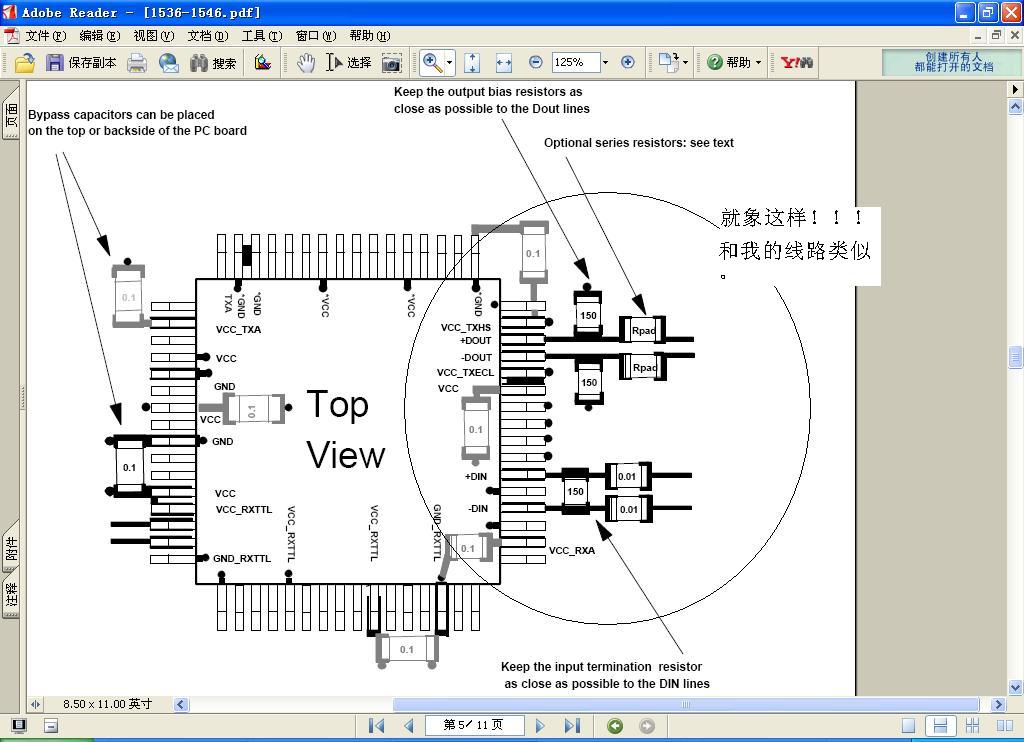

如图所示,整个线路板就上面的两对信号是1G,其他都是100M以内的信号,我以前顶多设计过100M的信号,对高速布线也没太在意,现在直接遇到了1G.我的PCB为4层,我计划把该差分信号放在表层,因为元件在表层,不用过孔.表层为信号层,中间层1为GND,中间层2也为GND,底层为信号层.线路要求50欧姆的阻抗,芯片之间的距离估计在1000MIL左右,请问线宽12MIL可以吗?差分信号的两边和中间可以敷铜(GND)吗?下载了阻抗计算器,但是影响反射和干扰的因素太多不好计算.请高人指点.

这种信号要求两个参考平面,严格等长,中间最好不要换层。严格控制阻抗。差分与其他信号线距离足够就ok。

一个参考层足够了,因为是在表层,即使在内层也很少用两个参考层,差分线不要参考层也可以的,不过你要选用合适的模型把阻抗计算好了,这里差分阻抗应该是100欧姆才对啊

12MIL线太宽了,建议改细点,这样差分线间距可以小点,表层到参考层的距离可以小点,这样可以减小串扰(主要是差分线干扰其他线)

另外,建议把其中一个GND层改为电源层

谢谢楼上的2位,我明天要和制板商联系一下,据说他们可以对阻抗进行控制.另外我想请问,如果我的连线不多的话是否可以布双层板?TOP曾为信号和电源,底层为GND.这样能做阻抗控制吗?对于终端的上拉电阻和下拉电阻,是采用T形连接,还是采用Y形连接?还是信号线先到终端,再从终端连线到电阻(即用一条线把终端和电阻串起来)?应该注意什么事项?还有就是差分线的中间和两侧能否用覆铜(GND)?

最好用SPECCTRAQUEST仿真一下,否则,可能有问题!

如果线不多,当然可以做两层,也可以做阻抗控制,差分对看的是差分阻抗,所以这里的50说的不够准确,在控制差分阻抗时,线宽和对线间的距离是关键,为保证信号质量(10mil以下),尽量增大差分对与其他信号间的距离(20mil以上),这些数据不准确,因为我不知道你的叠层。

走在表层当然可以,而且小编分析的道理不错,再要关心的就是走线长度,如果你没有一个可以参考的设计指导,就只能自己去做仿真(想来小编是没有设计指导的,因为小编对端接如何做还不能确定),所以这里也无能为力,不过1000MIL左右,对差分信号来说,应该是没有问题的。

这种线我们做的较多,问题不大。

QQ:439437163

谢谢楼上几位,我和制造商联系过了,阻抗控制没问题,能够按照特征阻抗要求制作.

"对于终端的上拉电阻和下拉电阻,是采用T形连接,还是采用Y形连接?还是信号线先到终端,再从终端连线到电阻(即用一条线把终端和电阻串起来)?"

上面这些问题也要做仿真吗?

我认为端接电阻应放在接收终端之后

不要T型走线,这样不好控制。匹配电路尽可能靠近终端,电阻,电容到终端的连线要尽可能短。电阻,电容到地的引线尽可能短,不要链接其他地信号共用一个接地到内层。

谢谢各位,我看了相关设计资料,电阻,电容要求离匹配尽可能近.

不要怕,大胆地做,1GHz不像你想的那么难做。

4层板参考层结构为:信号(顶)、地平面、电源平面、信号(底)。各层间距依次可为10mil、40mil、10mil。

假定板材介电常数4.2,表层到参考层距离10mil,阻焊层厚1mil(介电常数4.2),差分对间距10mil,差分对铜厚1oz,则100欧姆差分线对宽度约10.5mil。

终端匹配电阻尽量靠近接收端即可。

受教乐

受教乐

知道了

了解了不少东西,受教了。

严重同意以上分析,这里高手如云哪!

严重不同意3楼高速信号关于差分线不需要参考平面的表述,,请注意不需要参考平面的适用条件,,在pcb板中基本上都是不满足的,具体请参考<信号完整性分析>一书......

to guan_2000

差分线中间当然不能铺gnd,,外侧,个人认为可以铺地,,但不能太近,,最好要比参分线到参考平面的高度距离远

同意ttl的看法.差分线也需要参考平面当回流路径的,

没做过1

个人观点:

1、对于GHz的信号,走线不能太细,至少大于8mil。减小介质损耗。减小集肤效应。因为GHz以上的时候,信号的衰减很厉害,而且是与介质和线宽很大的关系。

2、差分线对之间的间距最好是满足大于5倍的线间距。前提是该差分信号和GND层的介质较薄,目的是减小线间的共模干扰。

3、如果感兴趣可以做仿真,最好是用hspice搭建链路,看看走线的长度影响,最好是不要超过15inch。Cadence的仿真这样的信号,效果不是很好。

4、差分阻抗的控制一定要满足在2%范围内。

当然还有很多其他的因素。

GHz以上信号的布线,重点注意阻抗的不连续点,比如过孔、插件、连接器处,这些处理好了,就差不多了,长度要尽量短,差分对内的对称要做好,尽量走内层。