FPGA和DDR II内部都有odt作阻抗匹配,其原理是?

时间:10-02

整理:3721RD

点击:

是否就相当于末端的并联系匹配,并了二电阻,这样不会功耗增加吗?

高手说说

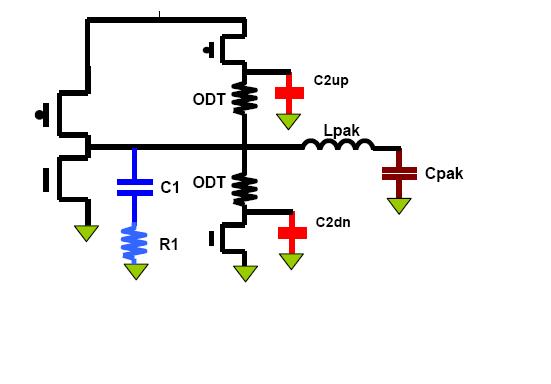

ODT的示意图如下.

OTD就是末端的并联匹配,其目的在与有最好的匹配,减少反射.

DDR SDRAM的主板上面为了防止数据线终端反射信号需要大量的终结电阻。

实际上,不同的内存模组对终结电路的要求是不一样的,

终结电阻的大小决定了数据线的信号比和反射率,终结电阻小则数据线信号反射低但是信噪比也较低;

终结电阻高,则数据线的信噪比高,但是信号反射也会增加。

因此主板上的终结电阻并不能非常好的匹配内存模组,还会在一定程度上影响信号品质。

DDR2可以根据自已的特点内建合适的终结电阻,这样可以保证最佳的信号波形。

使用DDR2不但可以降低主板成本,还得到了最佳的信号品质,

在保证信号完整性的前提下,并不会增加功耗,因为DDR就有,只是在主板上自己加.

果然牛。

1、那为什么cpu与北桥的高速总线没接匹配电阻?且双cpu共享总线的也没接?

2、芯片封装也有引出线,很细,和pcb的线接,就阻抗不连续了,这怎么解释?

3楼不错啊

DDRII也能做内阻匹配了

以前只知到RAMBUS 的XDR有内阻,PCB LAYOUT的福音啊

可以不用绕那么多的蛇行线做长度匹配啦