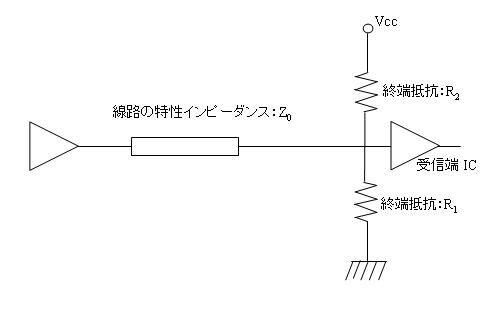

大家帮忙看看,这两种终端匹配,为什么第1种比第2种好呢?

大家帮忙看看,这两种终端匹配,为什么第1种比第2种好呢?

能否从原理上加以说明一下,谢谢。

1

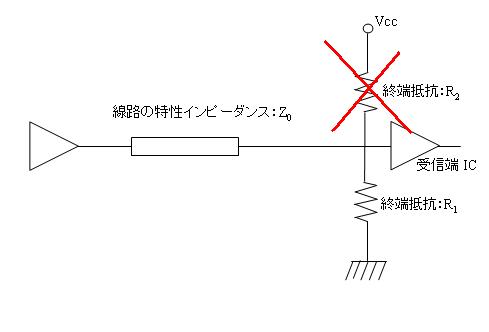

2

要保证接收端的高低电平都要满足要求

你的第一种是叫一种终端匹配,而你的第二种却不是终端匹配了,如果是的话,就应该还要加一个电容之后才能接地,

以下是引用yesok在2005-8-2 14:25:58的发言:

你的第一种是叫一种终端匹配,而你的第二种却不是终端匹配了,如果是的话,就应该还要加一个电容之后才能接地,

谢谢楼上的两位的回答。

关于第二种匹配,加不加电容我觉得都是终端匹配的方式,唯一不同点是,加了电容后,其消耗的电力将大大的减少罢了。

不知道大家是怎么认为的呢?

还有,第一种情况,是不是有高电平来了,通过上面的那个电阻接Vcc来保证长距离信号传送后到达接受端后还保持高电平状态;低电平也一样,通过下面那个电阻接地,保证到达接受端后依旧维持低电平状态呢?具体是如何实现的呢?因为同时存在一个Vcc和GND。怎么保证是拉高还是拉低啊?

因为根据分压原理,R1和R2之间是否电压一定?

谢谢大家再指教一下!谢谢!

第二种功耗太大,因为其电阻较第一种要 小,P=I*I*R较大

第一种的好处是可以有更大的noise margin,减小overshoot

第二种功耗更大?加电容是不是增加阻抗值,减小电流,从而使得P减小?

对于第一种有更大的躁声容限,减小过冲怎么理解?

奇怪,我怎么看两付图一模一样的

以下是引用aaronyhw在2005-8-2 15:22:59的发言:

谢谢楼上的两位的回答。

关于第二种匹配,加不加电容我觉得都是终端匹配的方式,唯一不同点是,加了电容后,其消耗的电力将大大的减少罢了。

不知道大家是怎么认为的呢?

还有,第一种情况,是不是有高电平来了,通过上面的那个电阻接Vcc来保证长距离信号传送后到达接受端后还保持高电平状态;低电平也一样,通过下面那个电阻接地,保证到达接受端后依旧维持低电平状态呢?具体是如何实现的呢?因为同时存在一个Vcc和GND。怎么保证是拉高还是拉低啊?

因为根据分压原理,R1和R2之间是否电压一定?

谢谢大家再指教一下!谢谢!

还没有人对此作出一个回答。

我看两副图也一样,怎么回事?

在没有详细器件参数特性的情况下,不能说哪一种就高明一些。

当然第一种,

第一种其实是两个电阻并联匹配,考虑电阻的误差并联后的误差要比单个电阻小。

另外一个作用是,不同类型的电平互联需要一个直流分压。

要看你的接收端器件跳变所需电流是否一样,如果H->L 不等于L->H,那么,R1和R2就不同,一般的TTL都是这样,而CMOS基本一样,要计算你所用的接收芯片到底要吸收或者释放多少电流。

我看也一样的

第一种确实很好,有一个缺点就是存在一个直流偏置。第二种方式不可能的,没有什么芯片有这么大的驱动能力。第一种为什么好,我也不知道,反正从仿真结果看,他很好,跟终端AC匹配差不多,好像还好一点。

恩,谢谢

如果是sdram 64bit数据线 20bit地址线 怎么进行第一种端接(split端接)

近百个电阻在电源和地之间并联,太可怕了,假设r1=r2=r,那么但条传输线带来电源和地之间并2r,如果84条传输线

那就是 2r/84=r/42,如果在让vcc/(r/42),在常规的r取值范围,这个电流将达到几安培!

是这样吗?那谁还敢采用这种端接?我对此不明白。大家以为呢

在以太网中,前一种端接很常见;如果不是特殊要求,采用第二种端接效果最好,但是对源端驱动电流比较大,自然也很耗电;所以折衷的方法是在终端的电阻串上一个电容的RC端接方式,这样就不会消耗直流功率了。如果要考虑到省电,那么最好是在源端串联电阻端接;这种方法最常见了。

楼上说的64 bit总线俺也没见过,估计只能采用最后一种方案了