设计验证时连接性检查错误都是+5V的过孔

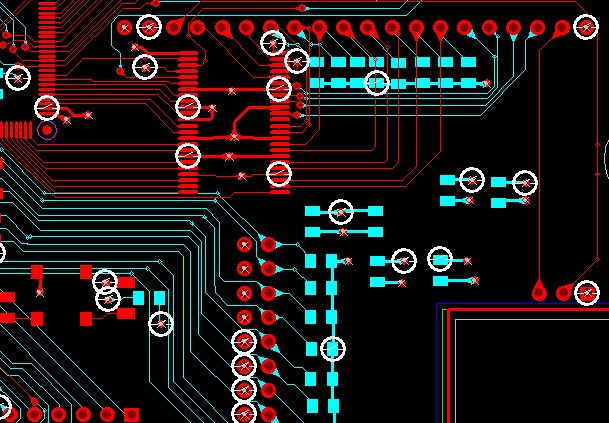

我在设计验证的连接性检查错误都是+5V和GND的过孔,不知道是什么原因?+5V是我电路中使用最多的电源.大概有100个错误都是因为+5V过孔和GND的过孔的原因,如下图(截取了一部分)请高手提醒啊!谢谢了.

我看了一下设计验证的explanition:Hatch outline(坐标)元件引脚 过孔(坐标)

没铺铜呀

连接性检查需要在铺铜之后吗?

如3楼所说

當然要啊!

多谢各位了,确实是铺铜之后再检查连接性.请问一下四层板,2层是GND,3层是power,铺铜时要铺几层呢?我是选中铺铜边框后右键选择铺铜,我的铺铜边框是在上层的,并且把GND网络添加在铺铜边框内了,为何要在铺铜边框内添加网络呢?困惑啊?

沒看懂樓上什么意思.

在tool->poul manager->plane connect里select all后再start就所有层都铺上了.

是这样的,我是先把电源层分割的,然后填充了电源层和底层,然后我在顶层又画了铺铜边框,画完后就弹出一Query/modify drafting对话框,在对话框的下半部分制定网络处我制定了GND,然后再选中铺铜边框点击右键后选择flood就填充了,我不明白为何画好铺铜边框后还要选择网络呢?还有最底层是不是也要铺铜呢?

不选择网络的話就是無网絡的銅.

底层一般鋪GND.

可是我是在顶层铺的铜啊,顶层铜的网络是GND,那是不是我在底层铺铜时铜的网络要选+5V啊?

你那個是什么板啊?为什么要在表层鋪電源?

那么tool->poul manager->plane connect里select all后再start铺铜就好了吗?select all内只power和gnd两层,是不是铺铜只是在power和gnd两层铺铜啊,顶层和底层不用铺铜啊?

上下两层看情况,元器件多密,可以不铺。否则还是铺好,都选GND网路。

你好厉害啊,一开始就弄那么复杂的4层板。建议最好先做简单的,如果有其它问题,是不怎么好修改。看你好像弄了好多天了吧。

是不是铺肯定比不铺好,为何上下两层铺铜都选GND网络呢?

當然要舖了

我知道了,如果元件很多的话可以不铺铜的,一般最好还是铺铜.我在顶层和底层都铺铜了,并且网络都是制定的GND.

to:FWX0506:确实是整了很久了,大家多帮忙~谢谢啊