数字时钟制作

时间:10-02

整理:3721RD

点击:

拿到板子已经有两个月了,非常感谢电子发烧友和小梅哥给予我这次使用机会,这两个月让我重新认识了FPGA,我对它不再是那么陌生了,现在才了解到原来FPGA是人工智能一个重要的发展方向,才发现它是硬件工程师必备的一项技能,现在做了数字时钟来检验这两个月的学习情况。

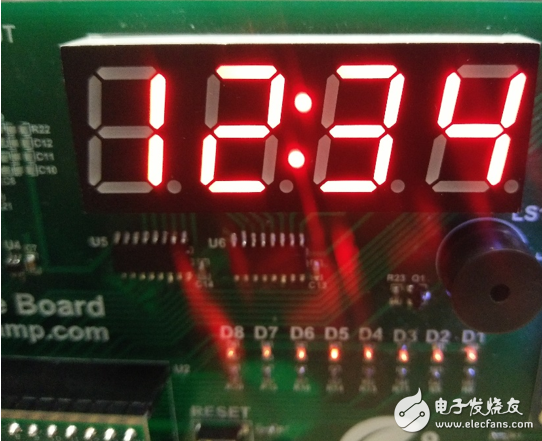

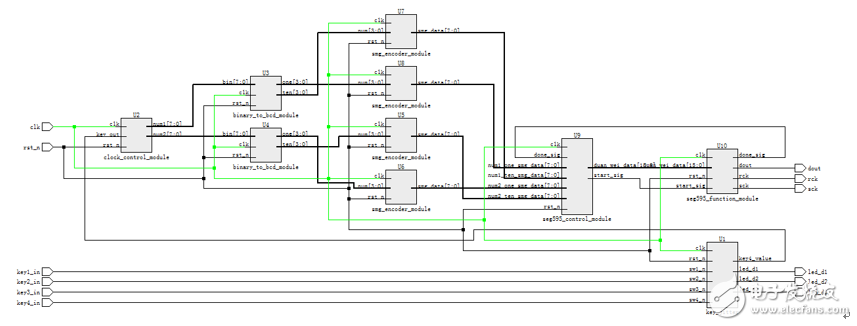

时钟显示设备采用共阳极数码管,时间显示格式采用24小时制,采用按键校准时间和设置闹钟,当闹钟响起时,蜂鸣器响持续10秒,后续可以加上解码功能,播放自己喜欢的音乐,时钟晶振采用和小梅哥一样的25MHz时钟晶振,K1,K2校准时间,K1调节十位,K2调节个位,K3进入闹钟设置,然后进行K1,K2设置,K4为确认键,数码管采用74CH5730芯片驱动,用计数器做分频处理,得到周期为一秒的脉冲信号,使用三个8bit的BCD码表示时钟,分钟,秒钟的值,其中高4bit表示值的十位,低4bit表示值的个位;每来一个1s脉信号个位加1,个位10清零同时十位加1,当秒针满60清零的同时,分针个位加1,当进行到23:59:59的下一刻全部清零。

最后做个小结:做这个行业,一定要有耐心,遇到困难不要急躁,一定要熟读技术手册,学会看技术手册是非常重要的,在做这个东西的过程中要特别感谢小梅哥的帮助,小梅哥逢问必答,非常贴心,太牛了。

最后再次感谢电子发烧友和小梅哥给予我这次使用机会,谢谢!

附上部分代码:

NOTE Copyright (C), 1992-2010, Lattice Semiconductor Corporation *

NOTE All Rights Reserved *

NOTE DATE CREATED: Wed May 04 15:22:58 2016 *

NOTE DESIGN NAME: Watch_system *

NOTE DEVICE NAME: LCMXO2-1200HC-4CSBGA132 *

NOTE PIN ASSIGNMENTS *

NOTE PINS key4_in : A11 : in *

NOTE PINS key3_in : A10 : in *

NOTE PINS key2_in : C8 : in *

NOTE PINS key1_in : B8 : in *

NOTE PINS rst_n : B1 : in *

NOTE PINS clk : C1 : in *

NOTE PINS alarm_beep : B2 : out *

NOTE PINS dout : K1 : out *

NOTE PINS rck : M1 : out *

NOTE PINS sck : N2 : out *

NOTE CONFIGURATION MODE: NONE *

NOTE COMPRESSION: on *

module Watch_system (clk, rst_n, key1_in, key2_in, key3_in, key4_in,

key5_in, sck, rck, dout, alarm_beep) /* synthesis syn_module_defined=1 */ ; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(18[8:20])

input clk; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(20[8:11])

input rst_n; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(21[8:13])

input key1_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(22[8:15])

input key2_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(23[8:15])

input key3_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(24[8:15])

input key4_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(25[8:15])

input key5_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(26[8:15])

output sck; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(27[9:12])

output rck; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(28[9:12])

output dout; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(29[9:13])

output alarm_beep; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(30[9:19])

wire clk_c /* synthesis SET_AS_NETWORK=clk_c, is_clock=1 */ ; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(20[8:11])

wire rst_n_c, key1_in_c, key2_in_c, key3_in_c, key4_in_c, key5_in_c,

alarm_beep_c;

wire [3:0]seg_flash_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(48[11:25])

wire [15:0]bcd_seg_display_num; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(49[12:31])

wire [7:0]num1_ten_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(62[12:29])

wire [7:0]num1_one_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(63[12:29])

wire [7:0]num2_ten_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(64[12:29])

wire [7:0]num2_one_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(65[12:29])

wire [15:0]duan_wei_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(99[12:25])

wire start_sig, done_sig, sck_c, rck_c, dout_c, Flag_1S;

wire [4:0]low_sw; // j:/step_demo_code/watch_system/impl1/source/key_jitter.v(48[10:16])

wire [4:0]low_sw_r; // j:/step_demo_code/watch_system/impl1/source/key_jitter.v(55[12:20])

wire GND_net;

时钟显示设备采用共阳极数码管,时间显示格式采用24小时制,采用按键校准时间和设置闹钟,当闹钟响起时,蜂鸣器响持续10秒,后续可以加上解码功能,播放自己喜欢的音乐,时钟晶振采用和小梅哥一样的25MHz时钟晶振,K1,K2校准时间,K1调节十位,K2调节个位,K3进入闹钟设置,然后进行K1,K2设置,K4为确认键,数码管采用74CH5730芯片驱动,用计数器做分频处理,得到周期为一秒的脉冲信号,使用三个8bit的BCD码表示时钟,分钟,秒钟的值,其中高4bit表示值的十位,低4bit表示值的个位;每来一个1s脉信号个位加1,个位10清零同时十位加1,当秒针满60清零的同时,分针个位加1,当进行到23:59:59的下一刻全部清零。

最后做个小结:做这个行业,一定要有耐心,遇到困难不要急躁,一定要熟读技术手册,学会看技术手册是非常重要的,在做这个东西的过程中要特别感谢小梅哥的帮助,小梅哥逢问必答,非常贴心,太牛了。

最后再次感谢电子发烧友和小梅哥给予我这次使用机会,谢谢!

附上部分代码:

NOTE Copyright (C), 1992-2010, Lattice Semiconductor Corporation *

NOTE All Rights Reserved *

NOTE DATE CREATED: Wed May 04 15:22:58 2016 *

NOTE DESIGN NAME: Watch_system *

NOTE DEVICE NAME: LCMXO2-1200HC-4CSBGA132 *

NOTE PIN ASSIGNMENTS *

NOTE PINS key4_in : A11 : in *

NOTE PINS key3_in : A10 : in *

NOTE PINS key2_in : C8 : in *

NOTE PINS key1_in : B8 : in *

NOTE PINS rst_n : B1 : in *

NOTE PINS clk : C1 : in *

NOTE PINS alarm_beep : B2 : out *

NOTE PINS dout : K1 : out *

NOTE PINS rck : M1 : out *

NOTE PINS sck : N2 : out *

NOTE CONFIGURATION MODE: NONE *

NOTE COMPRESSION: on *

module Watch_system (clk, rst_n, key1_in, key2_in, key3_in, key4_in,

key5_in, sck, rck, dout, alarm_beep) /* synthesis syn_module_defined=1 */ ; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(18[8:20])

input clk; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(20[8:11])

input rst_n; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(21[8:13])

input key1_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(22[8:15])

input key2_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(23[8:15])

input key3_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(24[8:15])

input key4_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(25[8:15])

input key5_in; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(26[8:15])

output sck; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(27[9:12])

output rck; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(28[9:12])

output dout; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(29[9:13])

output alarm_beep; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(30[9:19])

wire clk_c /* synthesis SET_AS_NETWORK=clk_c, is_clock=1 */ ; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(20[8:11])

wire rst_n_c, key1_in_c, key2_in_c, key3_in_c, key4_in_c, key5_in_c,

alarm_beep_c;

wire [3:0]seg_flash_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(48[11:25])

wire [15:0]bcd_seg_display_num; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(49[12:31])

wire [7:0]num1_ten_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(62[12:29])

wire [7:0]num1_one_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(63[12:29])

wire [7:0]num2_ten_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(64[12:29])

wire [7:0]num2_one_smg_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(65[12:29])

wire [15:0]duan_wei_data; // j:/step_demo_code/watch_system/impl1/source/watch_system.v(99[12:25])

wire start_sig, done_sig, sck_c, rck_c, dout_c, Flag_1S;

wire [4:0]low_sw; // j:/step_demo_code/watch_system/impl1/source/key_jitter.v(48[10:16])

wire [4:0]low_sw_r; // j:/step_demo_code/watch_system/impl1/source/key_jitter.v(55[12:20])

wire GND_net;

电源电路

蜂鸣器电路

按键电路

数码管电路

数字时钟设计框架

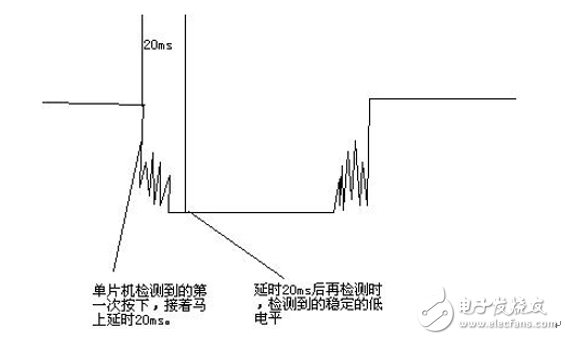

按键抖动特性

效果图