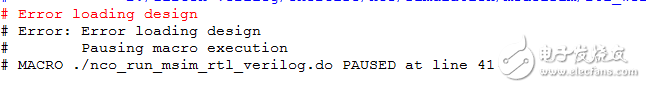

modelsim仿真nco核报错 Error loading design,显示do文件在执行第41行是停止

时间:10-02

整理:3721RD

点击:

情况是这样

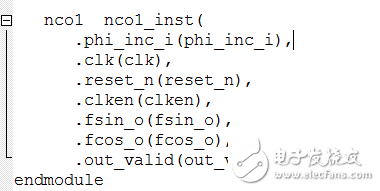

利用quartusII 13.1生成了一个nco 核,进行模块例化和tb文件编写

编译通过,没有问题,点击run rtl simulation,modelsim中仿真报错如图

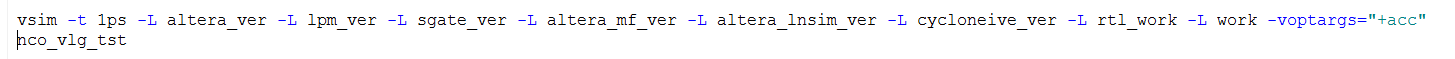

显示在执行nco_run_msim_rtl_verilog.do文件在第41行停止了,文件中的第41行如图

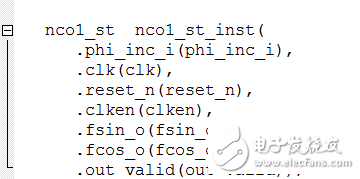

以前在仿真FIR核时出现过类似问题,我的解决方法是改掉模块例化名,原来的模块例化名如图

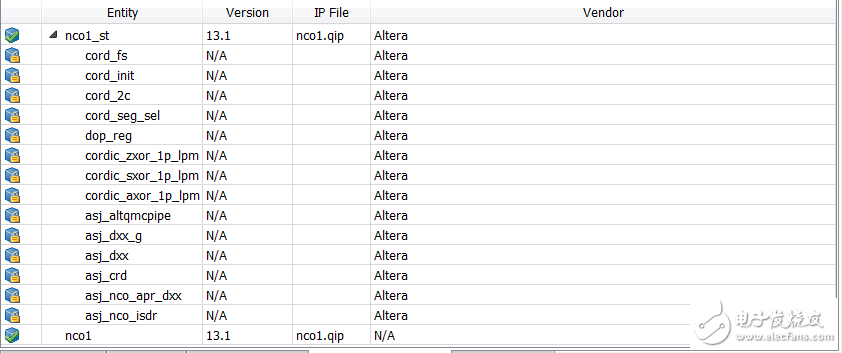

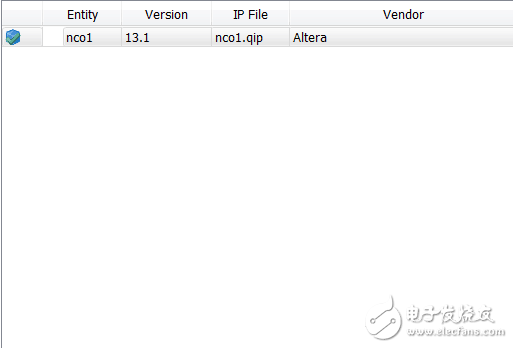

原来编译好的IP核如图

改正:将模块例化名中的 "_st" 删掉,改正后的模块例化名如图

编译后的IP核显示如图

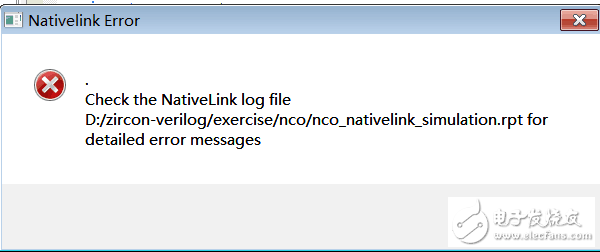

再次编译点击仿真,这回却报出了另外一个错误

错误中提到的文件内容粘贴如下

Info: Start Nativelink Simulation process

Error: You did not generate the simulation model files or you generated the IP file using an older version of MegaCore which is not supported by RTL NativeLink Simulation

Error: Regenerate the IP and simulation model files using the latest version of MegaCore for RTL NativeLink Simulation flow to function correctly

Error: NativeLink simulation flow was NOT successful

================The following additional information is provided to help identify the cause of error while running nativelink scripts=================

Nativelink TCL script failed with errorCode: NONE

Nativelink TCL script failed with errorInfo: Regenerate the IP and simulation model files using the latest version of MegaCore for RTL NativeLink Simulation flow to function correctly

(procedure "get_ip_info" line 1)

invoked from within

"get_ip_info $full_file_name"

(procedure "run_eda_simulation_tool" line 195)

invoked from within

"run_eda_simulation_tool eda_opts_hash"

编写的例化代码核tb代码如下

module nco (

phi_inc_i,

clk,

reset_n,

clken,

fsin_o,

fcos_o,

out_valid);

input [31:0] phi_inc_i;

input clk;

input reset_n;

input clken;

output [17:0] fsin_o;

output [17:0] fcos_o;

output out_valid;

nco1 nco1_inst(

.phi_inc_i(phi_inc_i),

.clk(clk),

.reset_n(reset_n),

.clken(clken),

.fsin_o(fsin_o),

.fcos_o(fcos_o),

.out_valid(out_valid));

endmodule

`timescale 1ps / 1ps

module nco_vlg_tst();

wire out_valid;

wire [17:0] sin_val;

wire [17:0] cos_val;

reg [31:0] phi;

reg reset_n;

reg clken;

reg clk;

parameter CYCLE = 20000;

parameter HALF_CYCLE = 10000;

initial

begin

$dumpvars;

#0 clk = 1'b0;

#0 reset_n = 1'b0;

#0 clken = 1'b1;

#0 phi = 32'b00000101000111101011100001010010;

#(14*HALF_CYCLE) reset_n = 1'b1;

end

always

begin

#HALF_CYCLE clk = 1;

#HALF_CYCLE clk = 0;

end

integer sin_ch, sin_print;

integer cos_ch, cos_print;

initial

begin

sin_ch = $fopen ("fsin_o_ver_nco1.txt");

cos_ch = $fopen ("fcos_o_ver_nco1.txt");

end

always @(posedge clk)

begin

if(reset_n==1'b1 & out_valid==1'b1)

begin

if (sin_val[17:0] < (1<<17))

sin_print = sin_val[17:0];

else

sin_print = sin_val[17:0] - (1<<18);

if (cos_val[17:0] < (1<<17))

cos_print = cos_val[17:0];

else

cos_print = cos_val[17:0] - (1<<18);

$fdisplay (sin_ch, "%0d", sin_print);

$fdisplay (cos_ch, "%0d", cos_print);

end

end

nco i_nco1 (

.out_valid(out_valid),

.fsin_o(sin_val[17:0]),

.fcos_o(cos_val[17:0]),

.phi_inc_i(phi[31:0]),

.reset_n(reset_n),

.clken(clken),

.clk(clk)

);

endmodule

不知道是哪里出了问题,所以求各位吧友指教,非常感谢!

暑假即将来临,想学习FPGA的同学们,可以利用暑假期间好好学习下FPGA,我们现在有款初学者的FPGA开发板利器,现在购买还有配套书籍赠送哦:

入门FPGA开发板:

https://item.taobao.com/item.htm ... &id=35911884243

赠送完全配套书籍:

https://item.taobao.com/item.htm ... amp;id=540865636294

有一定基础的同学,可以看下高端的开发板:

https://item.taobao.com/item.htm ... amp;id=520588767908

如果以上两款依然满足不了您的需求,更可以看下更高端的开发板:

https://item.taobao.com/item.htm ... &id=39939126777

有任何问题,欢迎旺旺 QQ来咨询哦!