Quartus17.0调用Modelsim仿真PLL无输出

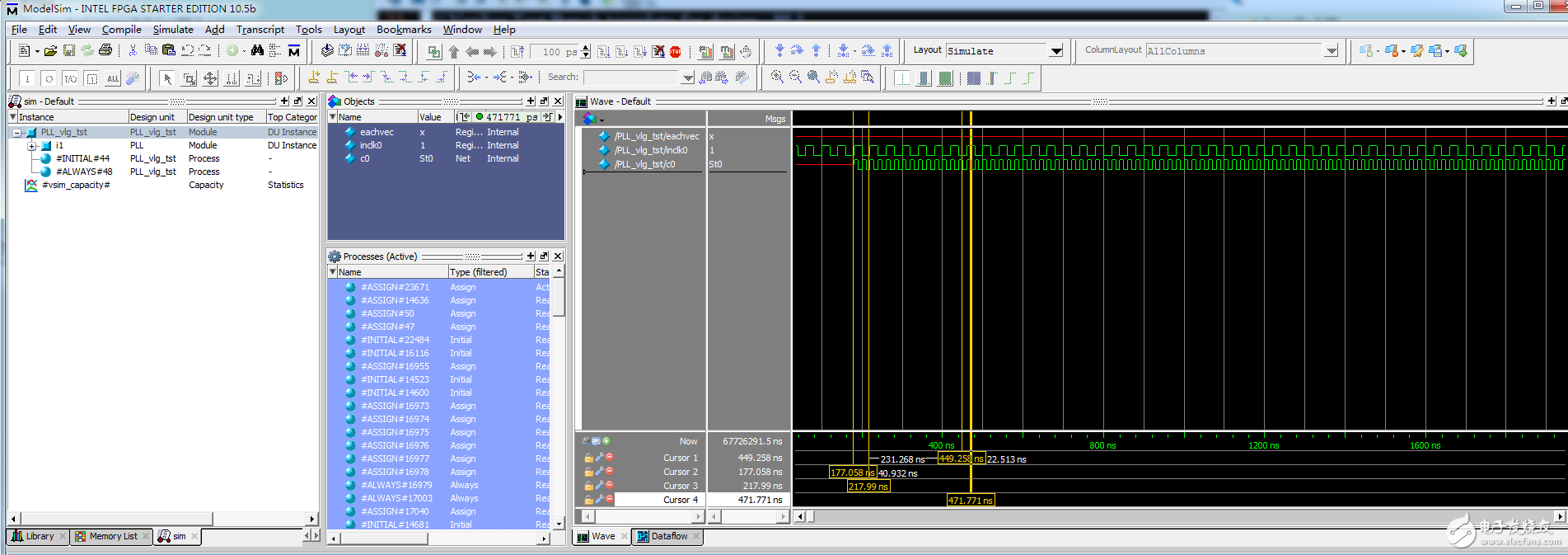

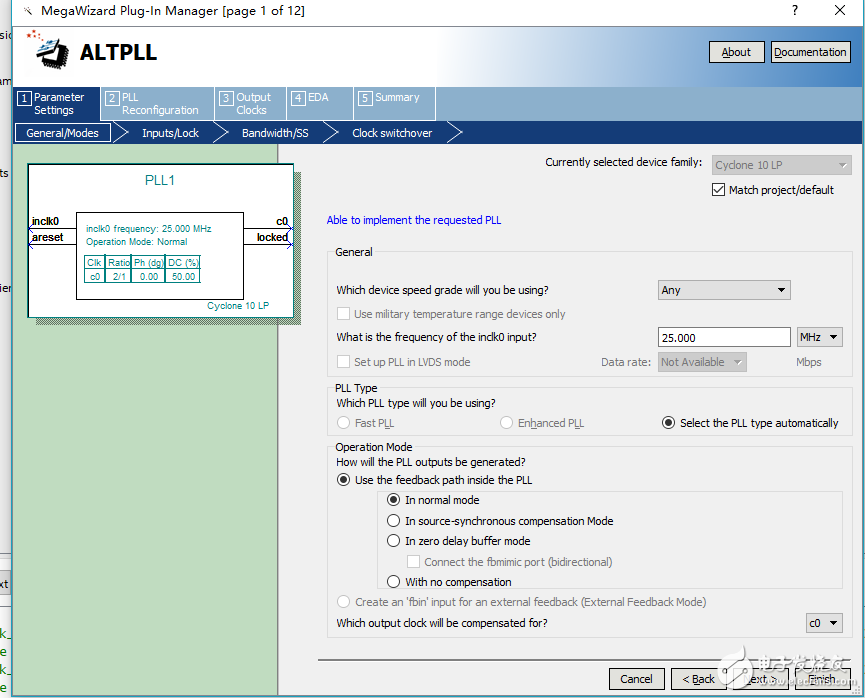

添加PLL的IP核,仿真的时候c0输出高阻,locked一直输出低;

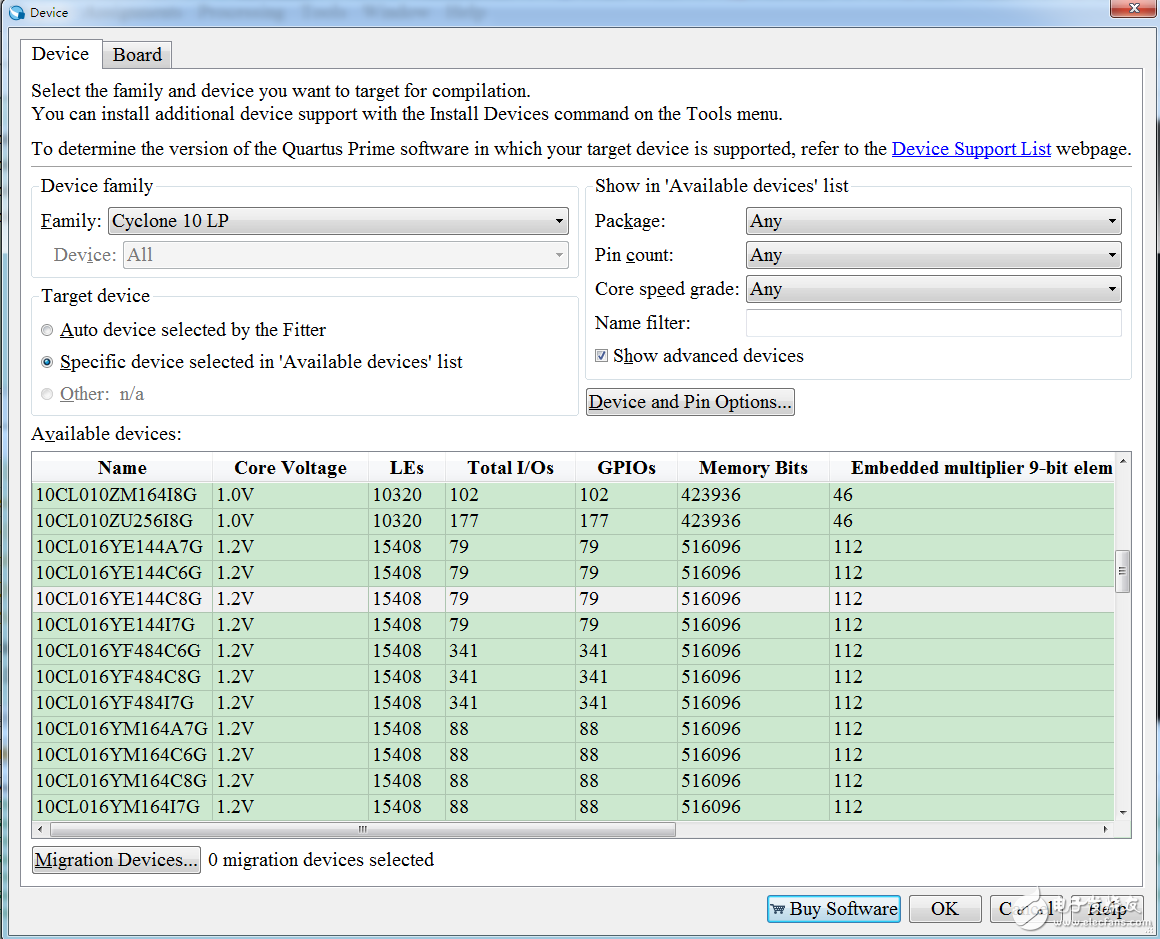

选用:Cyclone10的10CL016E144C8

目前尝试办法:

①选择Cyclone4的器件,调用C4的PLL IP仿真,IP可以正常仿真;

②更换Modelsim SE10.5(破解版),仿真c0输出高阻;

③安装Quartus17.0-stand(破解版),仿真c0输出高阻;

④自己重新编译了ModelSim的Altera库,依然c0输出高阻;

求大神指导指导。

注:目前器件不能变更,最终是要使用Cyclone10LP的,而目前只有Quartus17.0支持Cyclone10LP;

各位,再补一个顶层代码和testbench代码:

①top_pll3:

module top_pll3(

clk25M,

rst_n,

clk_50M,

locked

);

input clk25M;

input rst_n;

output clk_50M;

output locked;

wire clk_50M;

wire locked;

wire clk_c0;

PLL1 PLL_50M(

.areset (~rst_n),

.inclk0 (clk25M),

.c0 (clk_50M),

// .c1 (clk_200M)

.locked (locked)

);

endmodule

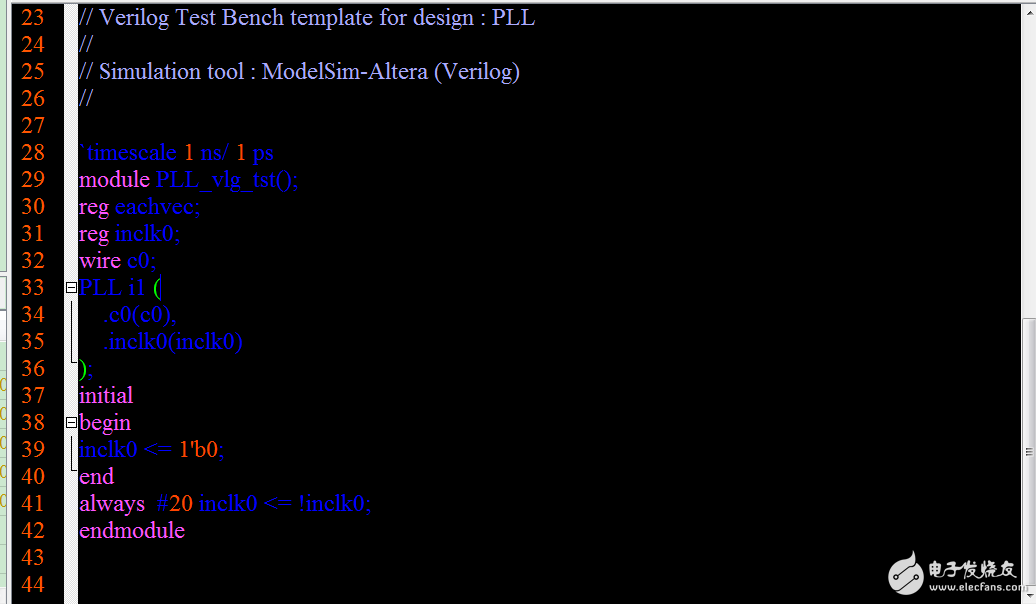

②testbench代码:

`timescale 1 ps/ 1 ps

module top_pll3_vlg_tst();

// constants

// general purpose registers

// test vector input registers

reg clk25M;

reg rst_n;

// wires

wire clk_50M;

wire locked;

// assign statements (if any)

top_pll3 i1 (

// port map - connection between master ports and signals/registers

.clk25M(clk25M),

.clk_50M(clk_50M),

.locked(locked),

.rst_n(rst_n)

);

initial begin

// Initialize Inputs

rst_n = 1'b1;

#10000;

rst_n = 1'b0;

#10000;

rst_n = 1'b1;

#10000;

/* rst_n = 1'b0;

#1000;

rst_n = 1'b1;

#1000; */

end

//clk initialzation

initial begin

clk25M = 1'b0;

forever

#20 clk25M = ~clk25M;

end

endmodule

没用过 帮你顶下

学习一下专业技能。

咨询过一些大牛,和多次尝试,问题出在软件上,正版的软件也没办法仿真。

目前一个比较折中的解决方案是:器件选10CL16型号,但是PLL选用Cyclone V的PLL库,是能够正常综合编译、仿真的。但这种办法还没有进行上板验证。

另外:过几天出新版17.1,到时候再尝试一下,看看是否可以解决,同时咨询技术支持,看看是否有合理的解释,后面有新结果了再更新,希望不要出现同样的坑。

你去掉复位引脚试试,IP设置去掉

尝试过了,也不行!通常去掉复位输入,pll的c0输出就变成不定值了

引脚绑定的对吗?板子上的晶振有没有起振啊

还处于仿真阶段呢。仿真的时候PLL无输出(输出高阻态)

最近Intel刚刚更新了Quartus17.1,我下载使用之后,发现还是PLL输出高阻态,总感觉是PLL核本身有问题,Intel的IP核某些状态位无法跳转导致的输出高阻。

测试文件输入激励不对吧,20ns对应50MHz,你例化的PLL输入是25MHz那么周期应该是40ns,而你的测试文件里面时间单位是ps周期是40ps,那么你的测试文件周期激励是25000MHz,所以与你当时例化是PLL的输入时钟不符合,将测试文件里面的时钟单位改了如`timescale 1 ps/ 1 ps 改成 `timescale 1 ns/ 1 ps应该就可以了,仅供参考

20ns反转,正反各反转一次才是一个周期,20ns对应是25MHz是没错的;

另外关于仿真时间设置,我之前设置过1ns/1ps,但输出没区别,后面就没有改了。仿真时间设置,我之前只是调整了testbench,以及软件里面的setup sim仿真设置,按你这一说,我是不是top、PLL模块里面的仿真时间没设置影响的呢?我回去再试一下给你答复,多谢你的建议。

我也是17.0,我直接把PLL例化作为了顶层仿真时可以的,应该是你仿真设置的不对。最直接的方法就是你把PLL的输入输出引脚绑定好,用示波器进行板载测试就知道了,手边没有示波器也可以使用signalTapII也可以的,只要有板子