NIOS II 上rom仿真问题

时间:10-02

整理:3721RD

点击:

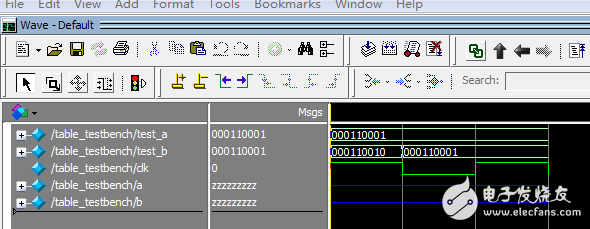

使用ModelSim对ROM进行仿真出现问题,仿真时系统未报错,只是无法读出数据。

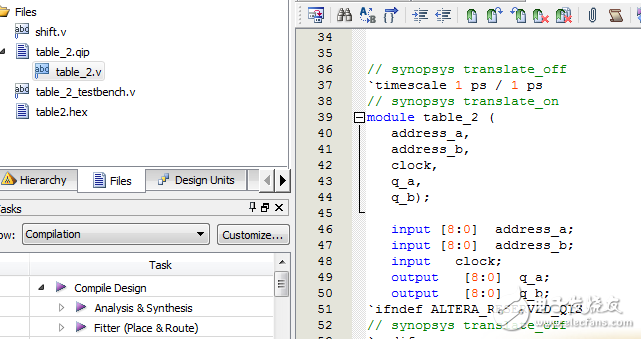

仿真的ROM:2—port

仿真文件

`timescale 1 ns/10 ps

module table_testbench;

localparam T=20;

reg [8:0] test_a,test_b;

reg clk;

wire [8:0] a,b;

table_2 table2(.address_a(test_a),.address_b(test_b),.clock(clk),.q_a(a),.q_b(b));

always

begin

clk=1'b1;

#(T/2);

clk=1'b0;

#(T/2);

end

initial

begin

test_a=9'h31;

test_b=9'h32;

@(negedge clk);

test_b=9'h31;

@(negedge clk);

$stop;

end

endmodule

请问到底该如何解决,会的人回答,因为网上各种方法都用过了,时钟找不到问题。

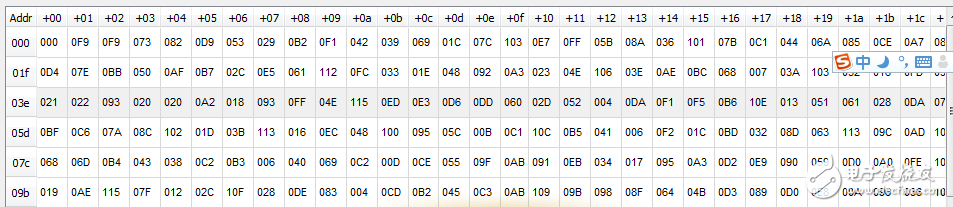

hex文件如下

512个字长为9bit

仿真的ROM:2—port

仿真文件

`timescale 1 ns/10 ps

module table_testbench;

localparam T=20;

reg [8:0] test_a,test_b;

reg clk;

wire [8:0] a,b;

table_2 table2(.address_a(test_a),.address_b(test_b),.clock(clk),.q_a(a),.q_b(b));

always

begin

clk=1'b1;

#(T/2);

clk=1'b0;

#(T/2);

end

initial

begin

test_a=9'h31;

test_b=9'h32;

@(negedge clk);

test_b=9'h31;

@(negedge clk);

$stop;

end

endmodule

请问到底该如何解决,会的人回答,因为网上各种方法都用过了,时钟找不到问题。

hex文件如下

512个字长为9bit

无法读取数据

rom

hex

已退回1积分