二 板卡细探(二)

接上篇“板卡细探(一)”,继续细探板卡硬件资源

存储器:

板卡上共有三种存储器:1)QSPI NOR FLASH,32MB;2)DDR3 SDRAM,256MB;3)I2C EEPROM

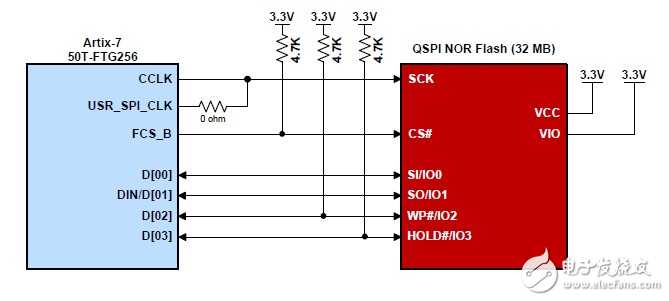

1) QSPI NOR FLASH:

如上节中讲到,FPGA启动时自动加载FLASH中程序,FPGA与FLASH之间通过QSPI通信,如下图

CCLK是FPGA上的专用时钟管脚,当配置完成后,自动切换成三态状态。

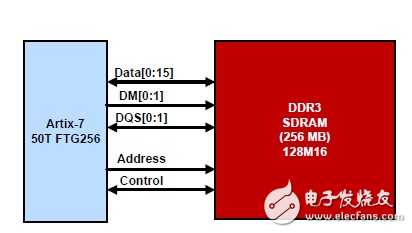

2) DDR3 SDRAM:

板载的DDR3 SDRAM芯片是来自Micron公司,型号MT41K128M16JT‐125 96‐ball FBGA封装,电压1.35V/1.5V, 数据吞吐率1600Mbps。

其与FPGA的接口如下图,主要引脚有:Data[0:15],DM[0:1],DQS[0:1],Address和Control

具体的FPGA引脚分配如下图

对应FPGA中的BANK 15,在进行FPGA设计时,可通过配置Memory Interface Generator (MIG)与DDR3的接口。

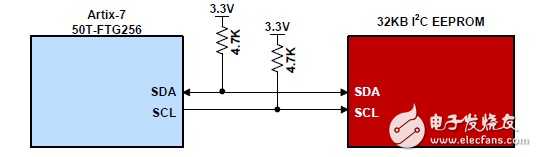

3) I2C EEPROM

板载EEPROM芯片ST Microelectronics M24C32 32KB I2C EEPROM,与FPGA连接的I2C接口如下图

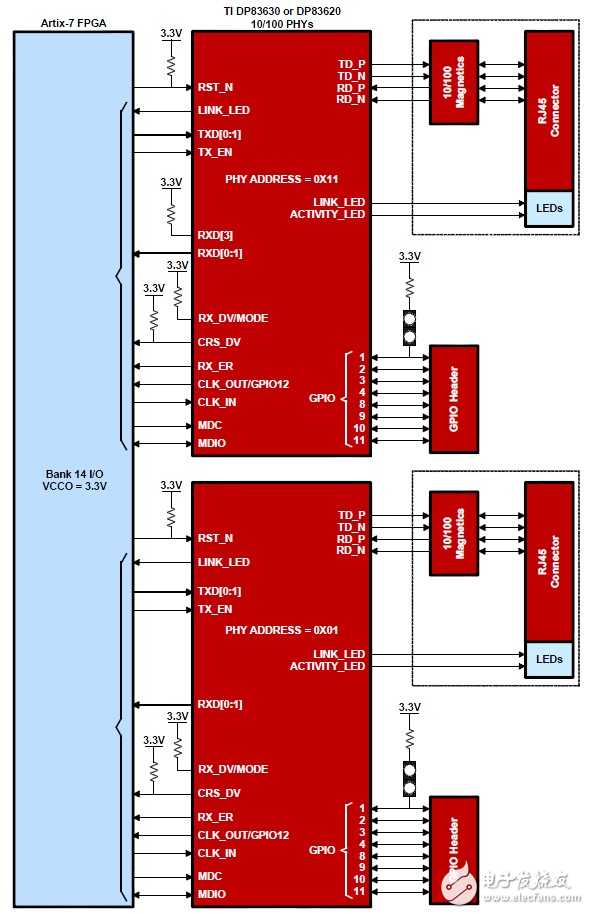

以太网

板卡自带双以太网接口,一般这种设计都是应用于工业以太网领域,如EtherCAT等。

两片以太网物理芯片都采用TI公司的DP83630,10/100Mbps数据传输,支持IEEE1588。PHY与FPGA的接口采用RMII (Reduced Media Independent Interface),其与MII接口相比,在保证相同数据吞吐率的基础上节省连接引脚。

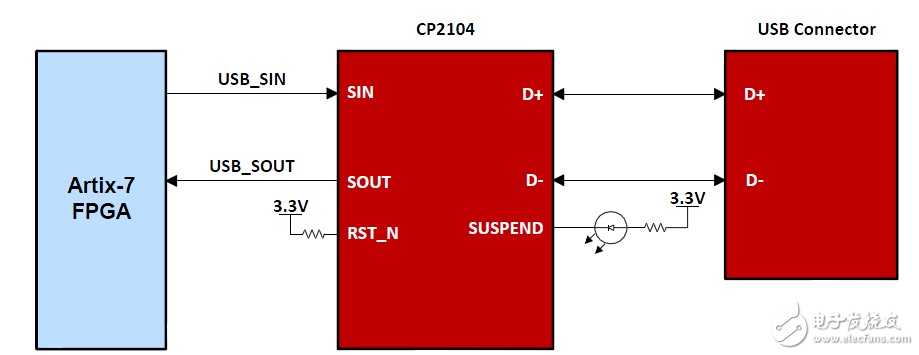

USB-TO-UART接口

上节中讲到板卡供电使用的USB口,此口还具有USB-TO-UART的功能。板载芯片Silicon Labs SiLabs CP2104将USB数据转换为串口数据,在FPGA端可简单作为UART设备进行处理即可,通信配置为115,200, 8, N, 1。

试用时间这周结束哦!请小编按要求提交结项报告了。