DDR2控制器集成与读写测试(一)

时间:10-02

整理:3721RD

点击:

本贴资料整理于《例说FPGA 可直接用于工程项目的第一手经验》

1.1功能概述:

对FPGA提供的DDR2控制器IP核模块进行读写操作。每1.78秒执行一次写入和读出操作。先从0地址开始遍历写256*64bit数据到DDR2的地址0-1023中;执行完写入后,执行一次相同地址的读操作,将读出的265*64bit数据写入到FPGA的片内RAM中。在Quartus II集成的In-System Memory Content Editor中可以查看片内RAM中规律变化的数据。

1.2 IP核配置——片内RAM

1.2.1 FPGA片内存储器概述

片内存储器是基于FPGA的嵌入系统中最简单的存储器。因为存储是在FPGA内部完成的,电路板上无需外部连线。FPGA片内存储器可以根据需求定义存储器的大小、位宽、种类及特殊的片内存储器特性,如DDR模式等。

片内存储器在基于FPGA的嵌入式系统的存储器中具有高吞吐量和最低反应延时。它的反应延时通常仅为一个时钟周期。同时片内存储器在一定程度上受到其容量的限制。FPGA可用的片内存储器的数量由所使用的特定FPGA器件决定。

因为多数片内存储器都是易失性的,它们在断电后会丢失数据。然而,某些片内存储器可以在FPGA配置时自动初始化,相当于提供了一种非易失性的功能。

片内存储器通常被用作常见的缓存、ROM、FIFO、移位寄存器等。

1.2.2 FPGA片内RAM概述

我们使用的Cyclone IV系列FPGA器件内嵌丰富的M9K存储器。有关M9K存储器的相关知识,请看我的帖子:

本实例我们要用Cyclone IV的片内存储器配置一个RAM。当然这里并非所有罗列的接口都用的到,除了写入数据总线data[]、地址总线address[]、写使能信号wren[]、写时钟inclock、读出数据总线q[]这几个接口外,其他接口都是可选接口。

1.2.3 FPGA片内RAM设置与集成

① Quartus II工程中,单击菜单Tools-MegaWizard Plug-In Manager命令,创建IP核模块。

② 在弹出的选项卡中选择“Create a new custom megafunction variation”,然后单击“Next”按钮

③ 在“Select a megafunction from the list below”下面的列表框中选择Ip核为“Memory Compiler-RAM:1-PORT”并选择好使用器件、语言以及工作路径,注意在工作路径后要加上IP核的名称。单击“Next”。

④ 在“How wide should the ‘q’ output bus be?”后面输入64,既该片内RAM的存储位宽是64bit

在“How many 64 bit words of Memory”后面输入256,既该片内RAM的存储深度为256words,此RAM的总容量为256*64bit

在“What should the memory block type be?”下面选择Auto,也可以选择M9K,表示我们使用的是FPGA中的Block RAM而不是LCs的DRAM。

在“What clocking method would you like to use”下面选择Single clock,表示该RAM读操作或者写操作使用一个时钟

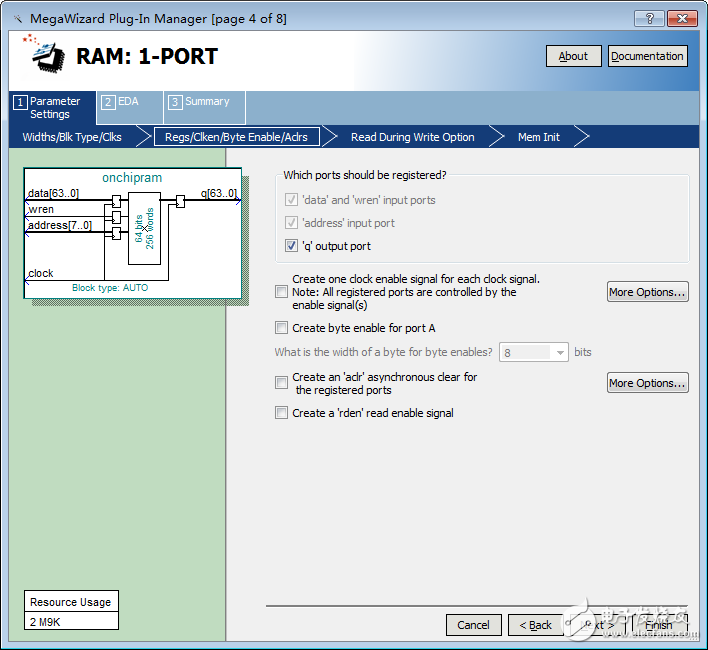

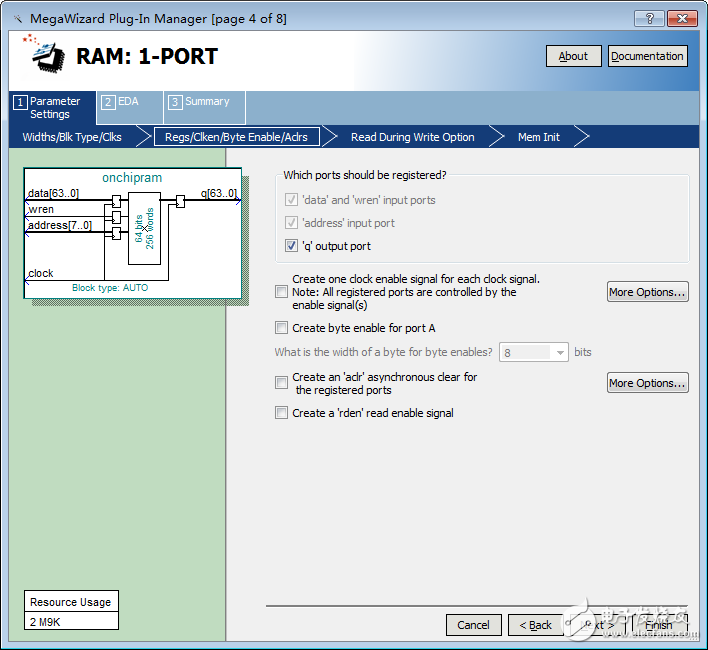

⑤ 在“Which ports should be registered”下面选择q output port,表示q信号输出时会用clock拍打一拍,这样更有利于时序收敛[使用registerd输出比输入延迟了两个周期。]。[为什么会有利于时序收敛?]

下面有创建时钟使能、字节选通、输入异步复位、读取使能选项,用户可以根据自己的需求使用相应的信号。

⑥ 在“what should the q output be when reading from a memory location being written to?”选择“new data”表示在同一地址读出的数据为刚刚写入的新的数据。如果选择“old data”表示在同一地址读出的数据为未写入之前的数据。

“get x’s for write mask bytes instead of old data when byte enable is used”目前还不清楚具体的含义,本例程中不使用byte enable,所以此处可以不用理会。

⑦ 在“Do you want to specify the initial content of the memory?”下面选择“No,leave it blank”表示我们不需要设置RAM的初始化文件。如果在别的场合需要初始化文件,则点击相应的选项并设置初始化文件路径即可。

在“Allow In-System Memory Content Editor to capture and updata content independently of the system clock”打勾,因为我们在板级调试时,需要使用In-System Memory Content Editor工具来实时查看RAM中内容的变化。

在“The ‘Instance ID’ of this RAM is”后面输入一个数字,代表此RAM的ID,它主要的功能是In-System Memory Content Editor工具区分查看不同的RAM。

⑧ 在“EDA”中Generate netlist选项可以产生时序和资源估计,在使用第三方EDA工具时,勾选此选项可以更好的优化设计。这里我们不使用第三方EDA工具故可以不勾选。

⑨ 最后产生实例化的模版文件,单击“Finish”

⑩ 我们可以看到,产生的VHDL源文件中包含有关的模块接口:

1.1功能概述:

对FPGA提供的DDR2控制器IP核模块进行读写操作。每1.78秒执行一次写入和读出操作。先从0地址开始遍历写256*64bit数据到DDR2的地址0-1023中;执行完写入后,执行一次相同地址的读操作,将读出的265*64bit数据写入到FPGA的片内RAM中。在Quartus II集成的In-System Memory Content Editor中可以查看片内RAM中规律变化的数据。

1.2 IP核配置——片内RAM

1.2.1 FPGA片内存储器概述

片内存储器是基于FPGA的嵌入系统中最简单的存储器。因为存储是在FPGA内部完成的,电路板上无需外部连线。FPGA片内存储器可以根据需求定义存储器的大小、位宽、种类及特殊的片内存储器特性,如DDR模式等。

片内存储器在基于FPGA的嵌入式系统的存储器中具有高吞吐量和最低反应延时。它的反应延时通常仅为一个时钟周期。同时片内存储器在一定程度上受到其容量的限制。FPGA可用的片内存储器的数量由所使用的特定FPGA器件决定。

因为多数片内存储器都是易失性的,它们在断电后会丢失数据。然而,某些片内存储器可以在FPGA配置时自动初始化,相当于提供了一种非易失性的功能。

片内存储器通常被用作常见的缓存、ROM、FIFO、移位寄存器等。

1.2.2 FPGA片内RAM概述

我们使用的Cyclone IV系列FPGA器件内嵌丰富的M9K存储器。有关M9K存储器的相关知识,请看我的帖子:

本实例我们要用Cyclone IV的片内存储器配置一个RAM。当然这里并非所有罗列的接口都用的到,除了写入数据总线data[]、地址总线address[]、写使能信号wren[]、写时钟inclock、读出数据总线q[]这几个接口外,其他接口都是可选接口。

1.2.3 FPGA片内RAM设置与集成

① Quartus II工程中,单击菜单Tools-MegaWizard Plug-In Manager命令,创建IP核模块。

② 在弹出的选项卡中选择“Create a new custom megafunction variation”,然后单击“Next”按钮

③ 在“Select a megafunction from the list below”下面的列表框中选择Ip核为“Memory Compiler-RAM:1-PORT”并选择好使用器件、语言以及工作路径,注意在工作路径后要加上IP核的名称。单击“Next”。

④ 在“How wide should the ‘q’ output bus be?”后面输入64,既该片内RAM的存储位宽是64bit

在“How many 64 bit words of Memory”后面输入256,既该片内RAM的存储深度为256words,此RAM的总容量为256*64bit

在“What should the memory block type be?”下面选择Auto,也可以选择M9K,表示我们使用的是FPGA中的Block RAM而不是LCs的DRAM。

在“What clocking method would you like to use”下面选择Single clock,表示该RAM读操作或者写操作使用一个时钟

⑤ 在“Which ports should be registered”下面选择q output port,表示q信号输出时会用clock拍打一拍,这样更有利于时序收敛[使用registerd输出比输入延迟了两个周期。]。[为什么会有利于时序收敛?]

下面有创建时钟使能、字节选通、输入异步复位、读取使能选项,用户可以根据自己的需求使用相应的信号。

⑥ 在“what should the q output be when reading from a memory location being written to?”选择“new data”表示在同一地址读出的数据为刚刚写入的新的数据。如果选择“old data”表示在同一地址读出的数据为未写入之前的数据。

“get x’s for write mask bytes instead of old data when byte enable is used”目前还不清楚具体的含义,本例程中不使用byte enable,所以此处可以不用理会。

⑦ 在“Do you want to specify the initial content of the memory?”下面选择“No,leave it blank”表示我们不需要设置RAM的初始化文件。如果在别的场合需要初始化文件,则点击相应的选项并设置初始化文件路径即可。

在“Allow In-System Memory Content Editor to capture and updata content independently of the system clock”打勾,因为我们在板级调试时,需要使用In-System Memory Content Editor工具来实时查看RAM中内容的变化。

在“The ‘Instance ID’ of this RAM is”后面输入一个数字,代表此RAM的ID,它主要的功能是In-System Memory Content Editor工具区分查看不同的RAM。

⑧ 在“EDA”中Generate netlist选项可以产生时序和资源估计,在使用第三方EDA工具时,勾选此选项可以更好的优化设计。这里我们不使用第三方EDA工具故可以不勾选。

⑨ 最后产生实例化的模版文件,单击“Finish”

⑩ 我们可以看到,产生的VHDL源文件中包含有关的模块接口: