用VHDL作了一个3相正弦波电路,波形老是有4个数值全为0的点,弄了半天了,求大神看看

时间:10-02

整理:3721RD

点击:

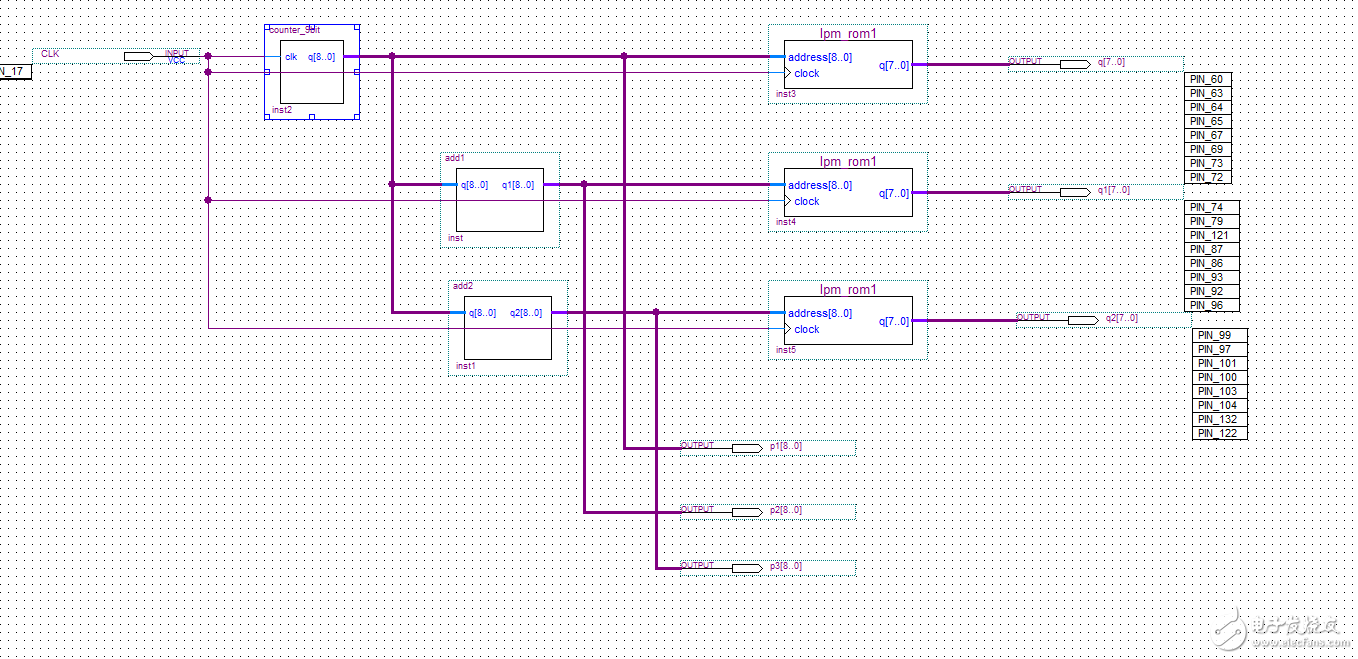

这是原理图,做的是360点的3相正弦波,就是每个输出的相位差120度

9位累加器代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter_9bit is

port( clk : in std_logic;

q : out std_logic_vector(8 downto 0)

);

end entity;

architecture one of counter_9bit is

signal p : std_logic_vector(8 downto 0):="000000000";

begin

process(clk)

begin

if clk'event and clk ='1'

then if p < "101100011" 数值355

then p <= p+1;q<=p;

else p <="000000000";q<=p;

end if;

end if;

end process;

end architecture;

地址移位器Add1代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity add1 is

port( q : in std_logic_vector(8 downto 0);

q1 : out std_logic_vector(8 downto 0)

);

end entity;

architecture one of add1 is

begin

process(q)

begin

if q < "0011101111" 数值119

then q1<=q+"011110000"; 数值120

else q1<=q-"001111000"; 数值240

end if;

end process;

end architecture;

地址移位器add2代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity add2 is

port( q : in std_logic_vector(8 downto 0);

q2 : out std_logic_vector(8 downto 0)

);

end entity;

architecture one of add2 is

begin

process(q)

begin

if q < "011110111" 数值239

then q2<=q+"001111000"; 数值120

else q2<=q-"011110000" ; 数值240

end if;

end process;

end architecture;

modelsim仿真一下就能找到答案了吧,代码我只看得懂Verilog的