求助,请问我设计的一个检测按键序列程序为什么不好用呢?

时间:10-02

整理:3721RD

点击:

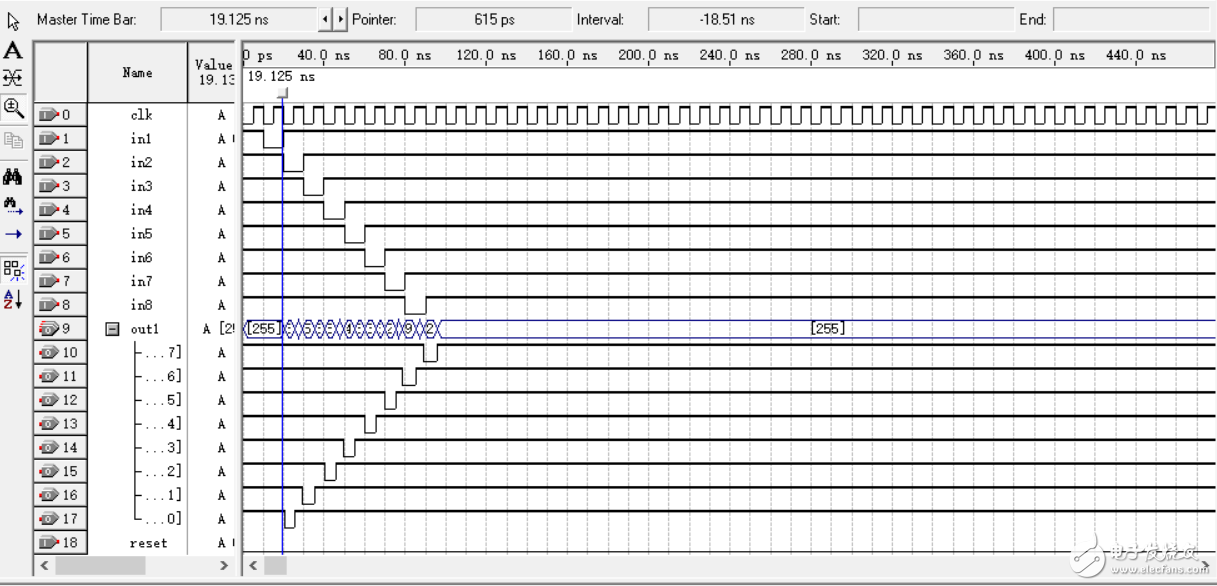

我设计的思路是用一个状态机,然后当我按照特定的顺序在一些管脚输入低电平时,可以在相应的管脚输出低电平,仿真也是好用的,但是现在我按下第一个按键的时候可以正确输出低电平,(在没有松开第一个按键时候)再按下第二个按键,第二个按键没有办法输出低电平,(此时松开第一个按键)仍然无法在第二个按键上检测到低电平?是我的频率的问题吗?主要想让我的51单片机可以正确检测到FPGA输出一个低电平后有一些后续的操作,但是现在FPGA不好使?请问大家能帮我看看嘛?另附仿真图,麻烦大家了。[qq]294108971[/qq]

- library ieee;

- use ieee.std_logic_1164.all;

- use ieee.std_logic_unsigned.all;

- use ieee.std_logic_arith.all;

- entity mealy2 is

- port(clk,in1,in2,in3,in4,in5,in6,in7,in8,reset : in std_logic;

- out1: out std_logic_vector(7 downto 0));

- end mealy2;

- architecture behavior of mealy2 is

- type state_type is (s0,s1,s2,s3,s4,s5,s6,s7);

- signal state: state_type;

- begin

- p1: process(clk,reset)

- begin

- if reset='1'then

- state if in1='0' then

- state if in2='0' then

- state if in3='0' then

- state if in4='0' then

- state if in5='0' then

- state if in6='0' then

- state if in7='0' then

- state if in8='0' then

- state if in1='0' then

- out1 if in2='0' then

- out1 if in3='0' then

- out1 if in4='0' then

- out1 if in5='0' then

- out1 if in6='0' then

- out1 if in7='0' then

- out1 if in8='0' then

- out1<= "01111111";

-

- else

- out1<= "11111111";

- end if;

- end case;

- end process p2;

- end behavior;