新人请教一个关于除法器IP核的问题

时间:10-02

整理:3721RD

点击:

我希望将两个寄存器A和B内的值相除,商保存在寄存器c0中,于是写了如下代码(测试)

always@(posedge clk)

begin

A <= A+1;

B <= B+1;

end

div_1 div1(.denom(A),

.numer(B),

.quotient(c0),

.remain(),

.clock(clk));

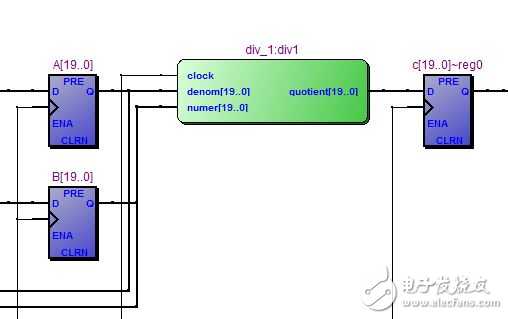

综合出来的RTL如图

可是,在时序检查时会提示Timing requirements not met.也就是寄存器A到寄存器c0的过程不满足时序要求,且仿真结果c0一直为0

另外如果直接将除法写成如下形式:

always@(posedge clk)

c0<= A/B;

就不会出现这样的问题,仿真结果也正常了,请问这是为什么?如何正确使用除法器IP核?

先行谢过了!

always@(posedge clk)

begin

A <= A+1;

B <= B+1;

end

div_1 div1(.denom(A),

.numer(B),

.quotient(c0),

.remain(),

.clock(clk));

综合出来的RTL如图

可是,在时序检查时会提示Timing requirements not met.也就是寄存器A到寄存器c0的过程不满足时序要求,且仿真结果c0一直为0

另外如果直接将除法写成如下形式:

always@(posedge clk)

c0<= A/B;

就不会出现这样的问题,仿真结果也正常了,请问这是为什么?如何正确使用除法器IP核?

先行谢过了!

但现在问题是我使用除法器时会提示时序不满足要求,而且输出恒为零……为什么会这样?

这应该是非常基本的问题,但我已经卡在这里好久了,痛苦啊!各位大神,求助啊!

好的,谢谢啦。

IP核用起来好像BUG还是不少啊= =..

好的,谢谢啦。

IP核用起来好像BUG还是不少啊= =..