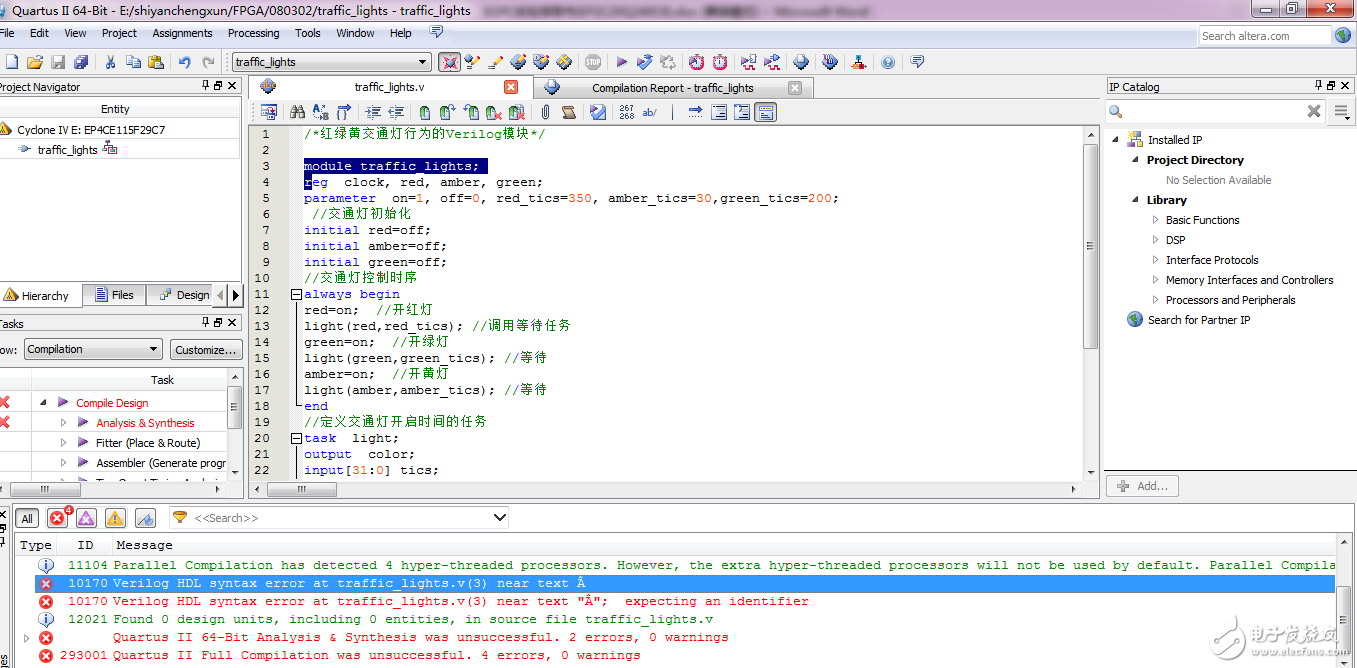

大神看看那里出了问题啊,红绿黄交通灯行为的Verilog模块

时间:10-02

整理:3721RD

点击:

/*红绿黄交通灯行为的Verilog模块*/

module traffic_lights;

reg clock, red, amber, green;

parameter on=1, off=0, red_tics=350, amber_tics=30,green_tics=200;

//交通灯初始化

initial red=off;

initial amber=off;

initial green=off;

//交通灯控制时序

always begin

red=on; //开红灯

light(red,red_tics); //调用等待任务

green=on; //开绿灯

light(green,green_tics); //等待

amber=on; //开黄灯

light(amber,amber_tics); //等待

end

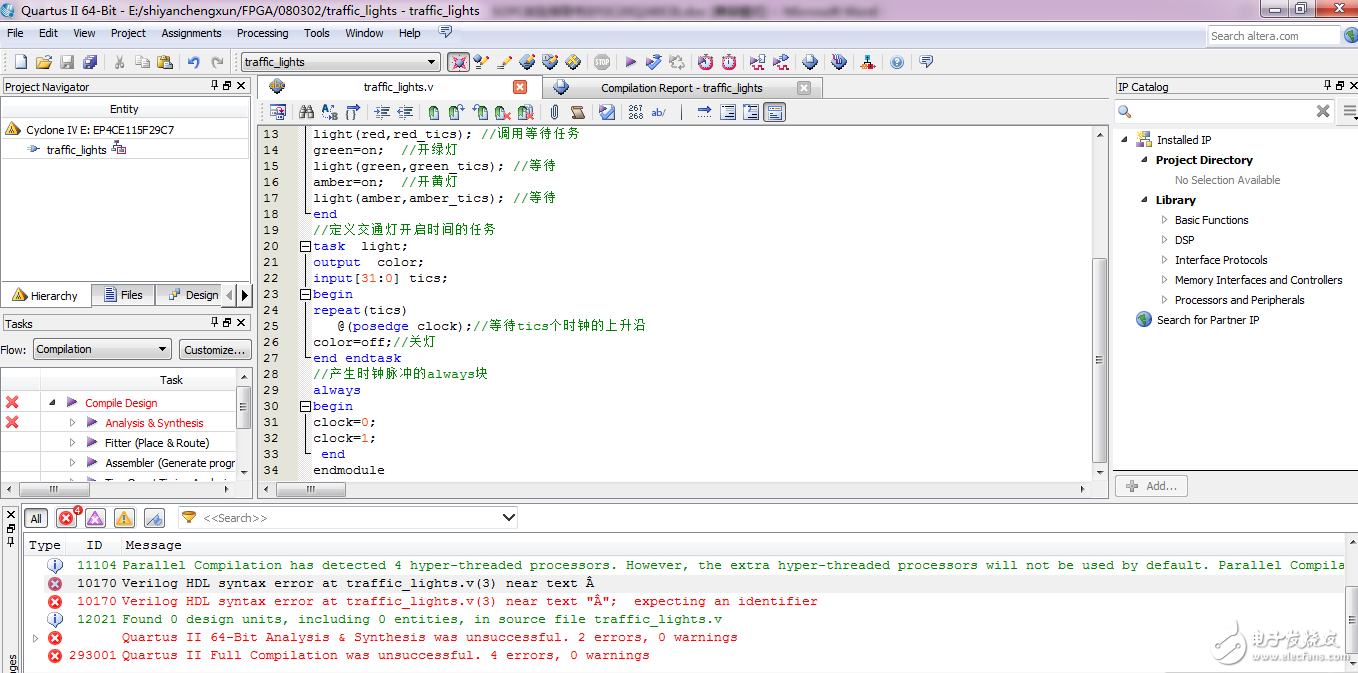

//定义交通灯开启时间的任务

task light;

output color;

input[31:0] tics;

begin

repeat(tics)

@(posedge clock);//等待tics个时钟的上升沿

color=off;//关灯

end endtask

//产生时钟脉冲的always块

always

begin

clock=0;

clock=1;

end

endmodule

module traffic_lights;

reg clock, red, amber, green;

parameter on=1, off=0, red_tics=350, amber_tics=30,green_tics=200;

//交通灯初始化

initial red=off;

initial amber=off;

initial green=off;

//交通灯控制时序

always begin

red=on; //开红灯

light(red,red_tics); //调用等待任务

green=on; //开绿灯

light(green,green_tics); //等待

amber=on; //开黄灯

light(amber,amber_tics); //等待

end

//定义交通灯开启时间的任务

task light;

output color;

input[31:0] tics;

begin

repeat(tics)

@(posedge clock);//等待tics个时钟的上升沿

color=off;//关灯

end endtask

//产生时钟脉冲的always块

always

begin

clock=0;

clock=1;

end

endmodule

自己顶111111111111111111111111111111111111

不要让我觉得是在玩单机的啊啊啊啊啊啊啊啊!

不要让我觉得是在玩单机的啊啊啊啊啊啊啊啊!

我是菜鸟,看报错信息的话,是不是你在写前3行的时候输入法的全角半角曾经切换过?试试重新打一遍前三行,看看行不行。

试过了,,不行啊