菜鸟求救:如何使用ISE中IP核生成的FIFO和RAM读写图像数据?

时间:10-02

整理:3721RD

点击:

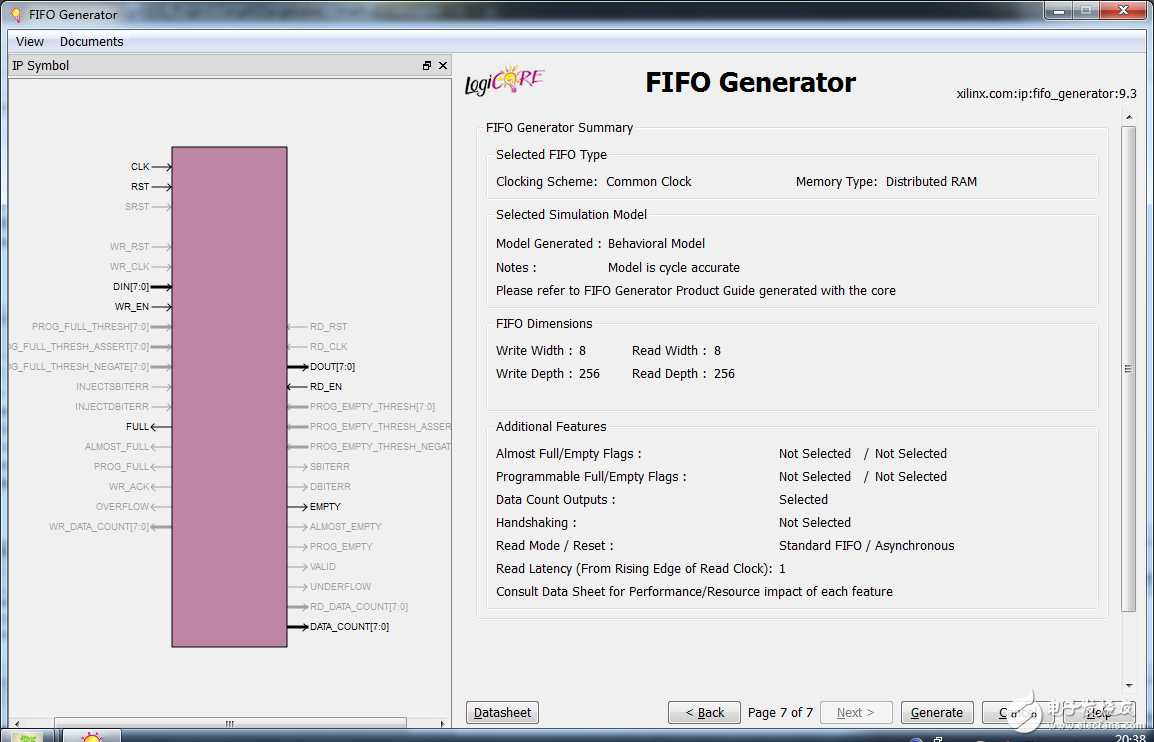

FIFO生成的例化代码:

FIFOS Import (

.clk(clock), // input clk

.rst(reset), // input rst

.din(din), // input [7 : 0] din

.wr_en(wr_en), // input wr_en

.rd_en(rd_en), // input rd_en

.dout(dout), // output [7 : 0] dout

.full(full), // output full

.empty(empty), // output empty

.data_count(data_count) // output [7 : 0] data_count

);

RAM生成的例化代码:

RAM your_instance_name (

.a(a), // input [5 : 0] a

.d(d), // input [7 : 0] d

.clk(clk), // input clk

.we(we), // input we

.spo(spo) // output [7 : 0] spo

);

1. FIFO, first input first output,顾名思义:先进先出,适合用于不同峰值速率的转换时;

把它当成一个系统、有输入、有输出,虽然它可以处理不同峰值速率之间的传递、但是 输入输出的平均速率必须相等、最大偏移不能大于FIFO的长度。 这跟数据传输有关系,跟图像没关系。比较对你项目实际的说明:它可以作为你图像数据通信的一个桥梁;

2. 片内RAM,图像显示建议使用双口RAM。 一进一出。

显示方式很简单,T时间进出RAM调换,比如:

在时间0-T之间、显示器显示的是RAM_1的内容;数据传输写到RAM_2的内容,更新RAM_2;

到时间T-2T之间,显示器显示的是RAM_2的内容;数据传输写到RAM_1的内容,更新RAM_1;

以此类推....

(RAM_1和RAM_2可以用一个RAM管理,地址一个比特作为选择即可)

如此一来,同一个RAM地址没有同时读写的情况.

这就需要你合理的规划这个跳转时间间隙了.

以上为设计思路,实际电路还得自己看吧。在生成IPcore的向导中,可以调出文档来看各个模块的时序.

FIFO的写入和读出是相互独立的,所以我可以先wr_en拉高,然后就按照wr_clk的时钟进行写入,判断wr_almost_full信号为高的时候,在读一次就拉低wr_en,然后再相应的拉高rd_en,开始读信号,当rd_almost_empty为高的时候,再读一个数据就可以拉低rd_en,是这个过程吧?

你说的是它的使用方法,可以参考官方手册,不同设置,不能的性能