+两张图,看清时钟

时间:10-02

整理:3721RD

点击:

一直在看例程 ,但现例程中没有时钟的配置程序,一开始也没有在意,现在把例程都试差不多了,反回来想想,有点费解。

由于没有看视频,今天发现视频里有一节是讲时钟的,就下载下来看成了一下。还是挻详细的。

原来时钟的配置在gel文件中。

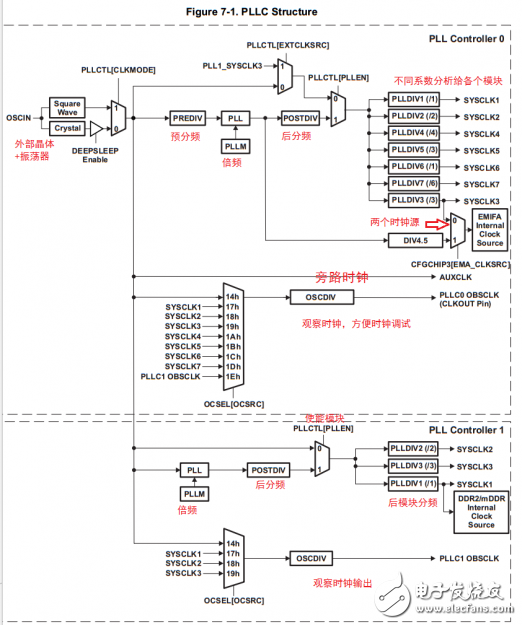

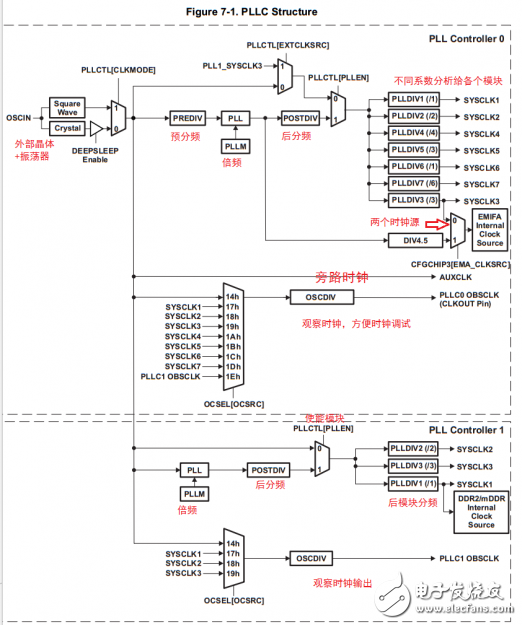

根据视频的讲解,做了下面两张图,算是把时钟部分的要点总结一下,再深入就是研究DSP的了,而我们这些只是会用就行了。

以下是两个时钟PLL0与PLL1的产生。

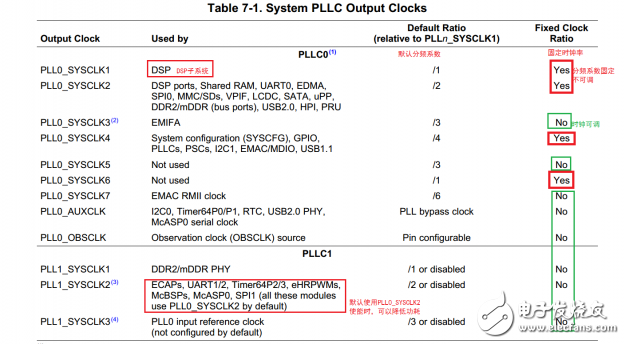

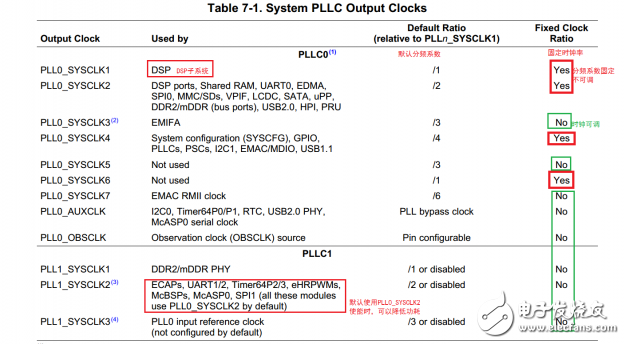

下面是两个时钟的一些参数。

之于时钟的配置可以在gel文件中的device_PLL0与device_PLL1两个函数中。

其实gel文件中所做的工作还是很多的。之前用28335的时候没怎么在意gel文件,所有的配置都是在C程序中的,看来有必要学习一下gel文件了。

由于没有看视频,今天发现视频里有一节是讲时钟的,就下载下来看成了一下。还是挻详细的。

原来时钟的配置在gel文件中。

根据视频的讲解,做了下面两张图,算是把时钟部分的要点总结一下,再深入就是研究DSP的了,而我们这些只是会用就行了。

以下是两个时钟PLL0与PLL1的产生。

下面是两个时钟的一些参数。

之于时钟的配置可以在gel文件中的device_PLL0与device_PLL1两个函数中。

- device_PLL0(unsigned int CLKMODE, unsigned int PLLM, unsigned int POSTdiv,unsigned int PLLdiv1, unsigned int PLLdiv2, unsigned int PLLdiv3, unsigned int PLLdiv7 ) {

- unsigned int i=0;

- /* Clear PLL lock bit */

- CFGCHIP0 &= ~(0x00000010);

- /* Set PLLENSRC '0',bit 5, PLL Enable(PLLEN) selection is controlled through MMR */

- PLL0_PLLCTL &= ~(0x00000020);

- /* PLLCTL.EXTCLKSRC bit 9 should be left at 0 for Freon */

- PLL0_PLLCTL &= ~(0x00000200);

- /* Set PLLEN=0 to put in bypass mode*/

- PLL0_PLLCTL &= ~(0x00000001);

- /*wait for 4 cycles to allow PLLEN mux switches properly to bypass clock*/

- for(i=0; i<PLLEN_MUX_SWITCH; i++) {;}

- /* Select the Clock Mode bit 8 as External Clock or On Chip Oscilator*/

- PLL0_PLLCTL &= 0xFFFFFEFF;

- PLL0_PLLCTL |= (CLKMODE << 8);

- /*Clear PLLRST bit to reset the PLL */

- PLL0_PLLCTL &= ~(0x00000008);

- /* Disable the PLL output*/

- PLL0_PLLCTL |= (0x00000010);

- /* PLL initialization sequence

- Power up the PLL by setting PWRDN bit set to 0 */

- PLL0_PLLCTL &= ~(0x00000002);

- /* Enable the PLL output*/

- PLL0_PLLCTL &= ~(0x00000010);

- /*PLL stabilisation time- take out this step , not required here when PLL in bypassmode*/

- for(i=0; i<PLL_STABILIZATION_TIME; i++) {;}

- /*Program the required multiplier value in PLLM*/

- PLL0_PLLM = PLLM;

- /*If desired to scale all the SYSCLK frequencies of a given PLLC, program the POSTdiv ratio*/

- PLL0_POSTdiv = 0x8000 | POSTdiv;

- /*Check for the GOSTAT bit in PLLSTAT to clear to 0 to indicate that no GO operation is currently in progress*/

- while(PLL0_PLLSTAT & 0x1==1){}

- /*Program the RATIO field in PLLdivx with the desired divide factors. In addition, make sure in this step you leave the PLLdivx.DxEN bits set so clocks are still enabled (default).*/

- PLL0_PLLdiv1 = 0x8000 | PLLdiv1; // Fixed Ratio /1

- PLL0_PLLdiv2 = 0x8000 | PLLdiv2; // Fixed Ratio /2

- PLL0_PLLdiv4 = 0x8000 | (((PLLdiv1+1)*4)-1); // Fixed Ratio /4

- PLL0_PLLdiv6 = 0x8000 | PLLdiv1; // Fixed Ratio /1

- PLL0_PLLdiv3 = 0x8000 | PLLdiv3; // Variable Ratio (EMIF)

- PLL0_PLLdiv7 = 0x8000 | PLLdiv7; // Variable Ratio (RMII)

- /*Set the GOSET bit in PLLCMD to 1 to initiate a new divider transition.*/

- PLL0_PLLCMD |= 0x1;

- /*Wait for the GOSTAT bit in PLLSTAT to clear to 0 (completion of phase alignment).*/

- while(PLL0_PLLSTAT & 0x1==1) { }

- /*Wait for PLL to reset properly.*/

- for(i=0; i<PLL_RESET_TIME_CNT; i++) {;}

- /*Set the PLLRST bit in PLLCTL to 1 to bring the PLL out of reset*/

- PLL0_PLLCTL |= 0x8;

- /*Wait for PLL to lock.*/

- for(i=0; i<PLL_LOCK_TIME_CNT; i++) {;}

- /*Set the PLLEN bit in PLLCTL to 1 to remove the PLL from bypass mode*/

- PLL0_PLLCTL |= 0x1;

- }

- /**********************************************************************************

- DDR PLL1 init:

- ***********************************************************************************/

- device_PLL1(unsigned int PLLM,unsigned int POSTdiv,unsigned int PLLdiv1, unsigned int PLLdiv2, unsigned int PLLdiv3 ) {

- unsigned int i=0;

- /* Clear PLL lock bit */

- CFGCHIP3 &= ~(0x00000020);

- /* Set PLLENSRC '0',bit 5, PLL Enable(PLLEN) selection is controlled through MMR */

- PLL1_PLLCTL &= ~(0x00000020);

- /* PLLCTL.EXTCLKSRC bit 9 should be left at 0 for Freon */

- PLL1_PLLCTL &= ~(0x00000200);

- /* Set PLLEN=0 to put in bypass mode*/

- PLL1_PLLCTL &= ~(0x00000001);

- /*wait for 4 cycles to allow PLLEN mux switches properly to bypass clock*/

- for(i=0; i<PLLEN_MUX_SWITCH; i++) {;}

- /*Clear PLLRST bit to reset the PLL */

- PLL1_PLLCTL &= ~(0x00000008);

- /* Disable the PLL output*/

- PLL1_PLLCTL |= (0x00000010);

- /* PLL initialization sequence

- Power up the PLL by setting PWRDN bit set to 0 */

- PLL1_PLLCTL &= ~(0x00000002);

- /* Enable the PLL output*/

- PLL1_PLLCTL &= ~(0x00000010);

- /*PLL stabilisation time- take out this step , not required here when PLL in bypassmode*/

- for(i=0; i<PLL_STABILIZATION_TIME; i++) {;}

- /*Program the required multiplier value in PLLM*/

- PLL1_PLLM = PLLM;

- /*If desired to scale all the SYSCLK frequencies of a given PLLC, program the POSTdiv ratio*/

- PLL1_POSTdiv = 0x8000 | POSTdiv;

- /*Check for the GOSTAT bit in PLLSTAT to clear to 0 to indicate that no GO operation is currently in progress*/

- while(PLL1_PLLSTAT & 0x1==1){}

- /*Program the RATIO field in PLLdivx with the desired divide factors. In addition, make sure in this step you leave the PLLdivx.DxEN bits set so clocks are still enabled (default).*/

- PLL1_PLLdiv1 = 0x8000 | PLLdiv1; // DDR frequency (aka 2X_CLK)

- PLL1_PLLdiv2 = 0x8000 | PLLdiv2; // Optional CFGCHIP3[ASYNC3_CLKSRC] clock source

- PLL1_PLLdiv3 = 0x8000 | PLLdiv3; // Optional PLL0 clock source

- /*Set the GOSET bit in PLLCMD to 1 to initiate a new divider transition.*/

- PLL1_PLLCMD |= 0x1;

- /*Wait for the GOSTAT bit in PLLSTAT to clear to 0 (completion of phase alignment).*/

- while(PLL1_PLLSTAT & 0x1==1) { }

- /*Wait for PLL to reset properly */

- for(i=0; i<PLL_RESET_TIME_CNT; i++) {;}

- /*Set the PLLRST bit in PLLCTL to 1 to bring the PLL out of reset*/

- PLL1_PLLCTL |= 0x8;

- /*Wait for PLL to lock. See PLL spec for PLL lock time*/

- for(i=0; i<PLL_LOCK_TIME_CNT; i++) {;}

- /*Set the PLLEN bit in PLLCTL to 1 to remove the PLL from bypass mode*/

- PLL1_PLLCTL |= 0x1;

- }

其实gel文件中所做的工作还是很多的。之前用28335的时候没怎么在意gel文件,所有的配置都是在C程序中的,看来有必要学习一下gel文件了。