设计中常见的线路工艺问题汇总

设计中常见的线路工艺问题汇总:

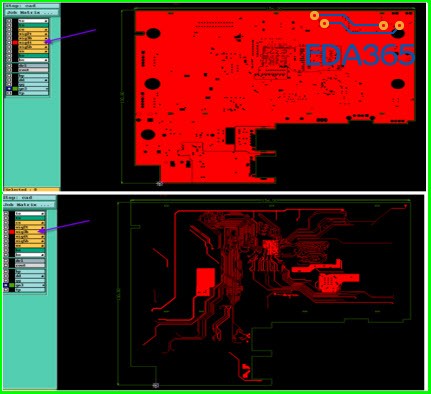

平面层:整层或层中某个分隔区域内没有网络连接。

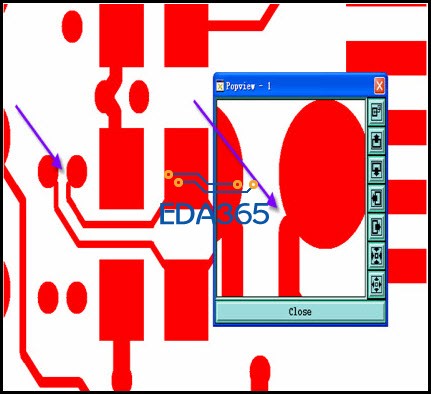

导通孔部分或全部打在隔离带或削铜的基材区上。

通道太小或没有通道,导通孔被堵死。

非金属化孔在铜皮上。

花焊盘内、外径大小或开口宽度设置不当。

负片层隔离带(区域分割线)丢失。

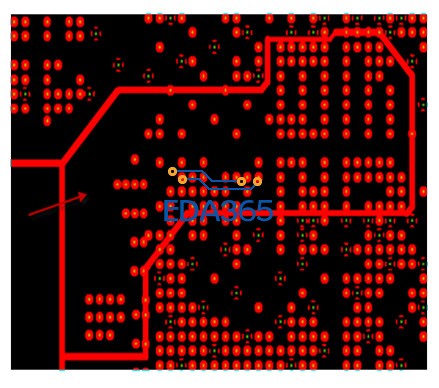

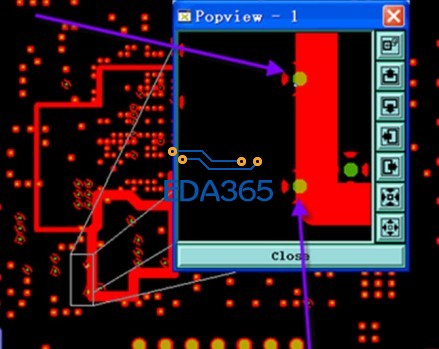

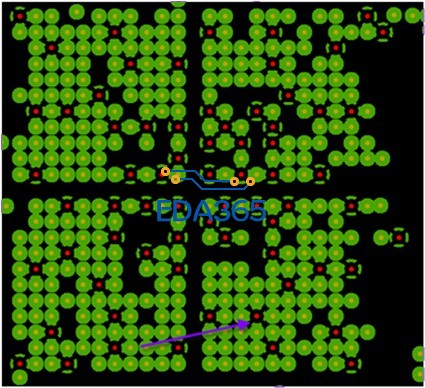

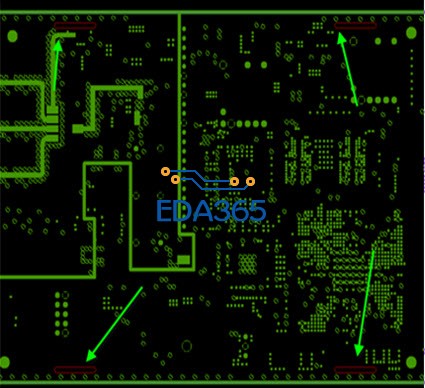

线路连接不良。

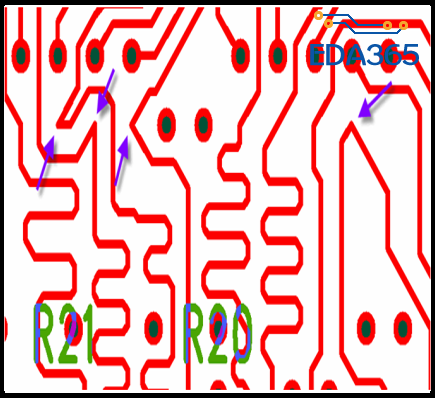

线歪、折线、直角、锐角走线。

重线、交叉线。

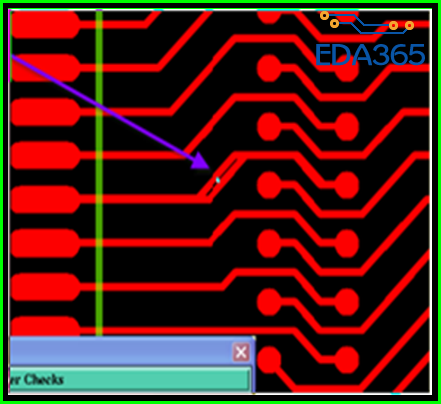

stub线(断线头) 。

同层阻抗线宽不一致。

差分线间距错误。

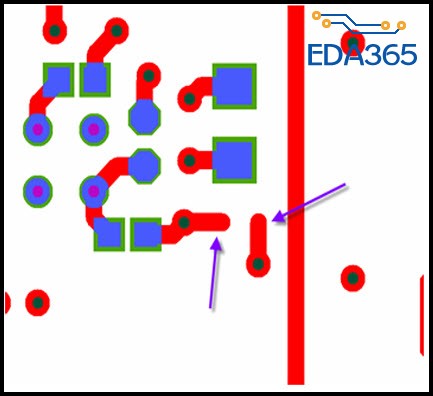

走线比焊盘宽或焊盘埋在铜皮里。

焊盘出线方式不当。

残铜率不对称。

阻抗线的屏蔽层不连续、不完整。

焊盘、线路等离板边太近或超出外形线。

外形中多余的线在每层文件中都有,其它层标识、线路等设错层。

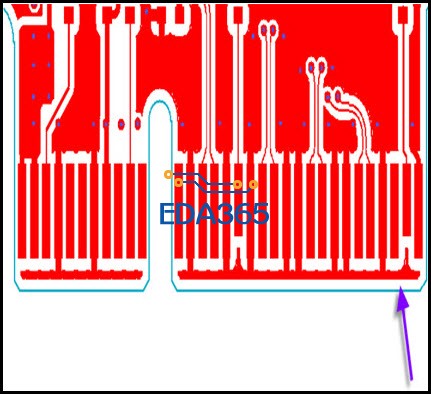

金手指区域铺了铜皮。

板边铜皮没有削铜。

板边有阻焊开窗,但对应的外层线路上没有铺铜。

走线问题

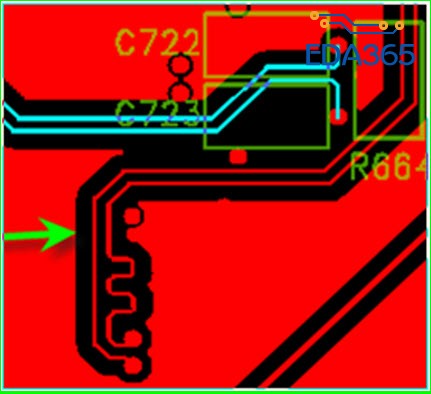

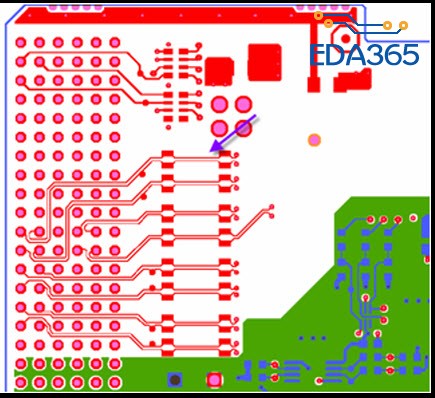

线路连接不良(protel,pads软件容易出现此类问题,其它软件有相关stub检查,较少出现。和设计习惯有很大关系。生产当中蚀刻后容易导致开路)

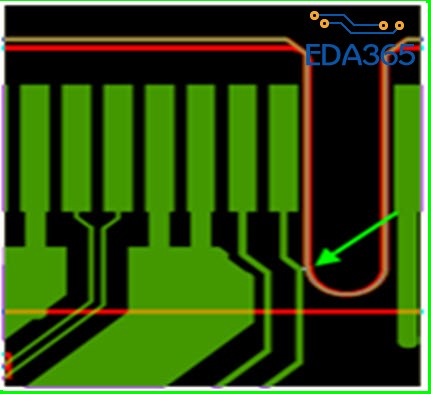

线歪、折线、直角、锐角走线(protel,pads软件容易出现此类问题。走线模式因需要切换了未切换回来,和设计习惯有很大关系。容易影响信号质量问题。)

重线、交叉线(走线模式未切换过来)

stub断线头,器件移开后未及时修线或走线当中移动过孔,未及时修线路。通常工厂端会确认,延误订单交付。

同层阻抗线宽不一致,规则设置不对或在走线当中更改了线宽设置。通常这样的问题工厂端会漏掉控制阻抗。

差分线间距错误(走线当中没有推挤好或规则设置有问题。通常工厂端不会理会,即走错了就控制不到阻抗了)

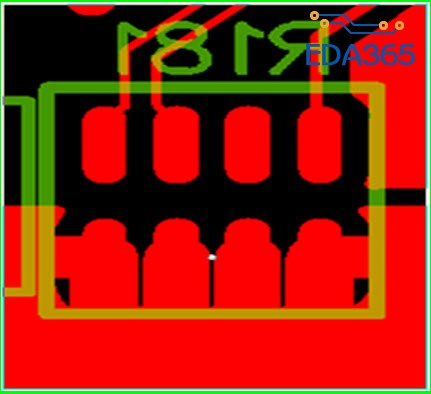

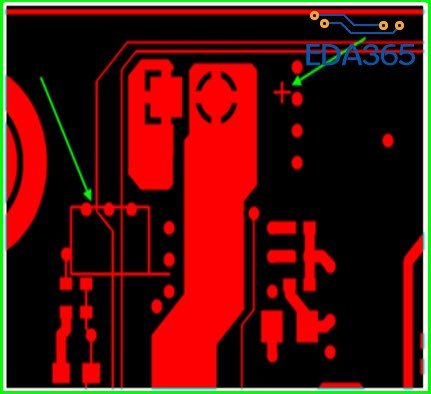

走线比焊盘宽或焊盘埋在铜皮里(规则未设置好或未设置局部keepout。影响焊接,如有特别器件可以例外)

焊盘出线方式不当(gap设置和走线不当。影响生产和焊接)

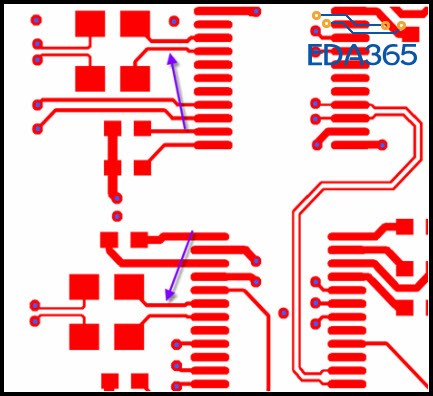

残铜不对称(影响板子翘曲。设计软件中未有此检查项,可以通过各自的编程skill实现)

阻抗线的屏蔽层不连续或没有屏蔽到(1电源分割时跨分割 2射频线隔层未注意到 3信号相邻时铺电源铜影响)

焊盘、线路等离板边太近或超出外形线(走线时注意设置keepout 如碰到特殊器件需要伸出板外,在文件中加个备注说明情况 避免加工进确认耽误时间)

其它线路问题

金手指位铺铜(生产时无法加上引线,手指镀不上金。使用时导致信号弹簧片短路 )

外形中多余的线(辅助线或结构导入到了边框层)

板边有阻焊开窗,但对应的外层线路上没有铺铜(这种情况生产厂家通常会反馈确认。如果反过来线路层有铜而没有开阻焊窗,通常生产厂家是不确认的,这样就达不到亮铜效果,或接触不了保护地、机壳地等)

小编好帖子,现在设计以及不单单死设计了,一定需要对工艺各种明白

区域内没有网络连接(大家探讨下是什么原因引起,什么软件比较容易出现这个问题,按道理有DRC检测,怎么会漏?是电源补强漏了,这样就不会报DRC开路)

孔打在隔离带上 生产当中会被工厂削开 间接的缩小了爬电间距

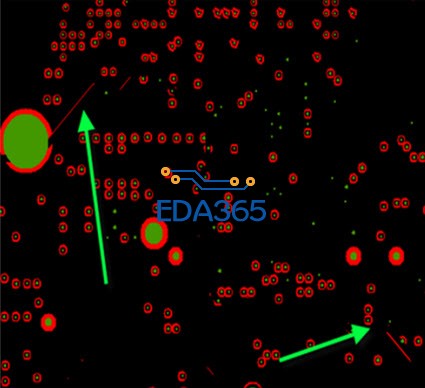

导通孔被堵死 这个问题通常在小间距封装器件内(0.4 0.5 0.65) 通常pcb软件不报drc,但实际效果是开路

非金属化孔或槽在平面层没有避让铜皮,通常是这种异形框或槽容易忘记在封装中设置避让铜皮(有些软件是直接在平面层增加区域避让,不是在封装中设置)。

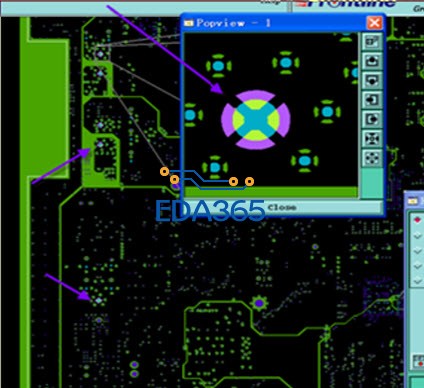

花焊盘内、外径大小或开口宽度设置不当。多数是封装设置不当,protel软件是规则设置不当。

负片层隔离带(区域分割线)丢失。容易出现在allegro软件中。

很给力!希望小编多分享,这个对设计帮助很大!

好帖子,必须顶,大家都多发表自己设计中的总结和经验,互相提高,好好学习,天天向上

各位大大功力深厚啊----------------

学习学习

确实啊,画板对工艺不了解很难画出好的作品

给力

赞一个

有总结,有实例,真正的好帖~~

另外求问下,“走线比焊盘宽或焊盘埋在铜皮里。” 这条,如果器件本身建议用铜皮辅助散热,那用上热风连接后的 宽走线或包围铜皮是否可接受呢?

学习学习

很给力!