自己仿得DDR2部分的串扰

时间:10-02

整理:3721RD

点击:

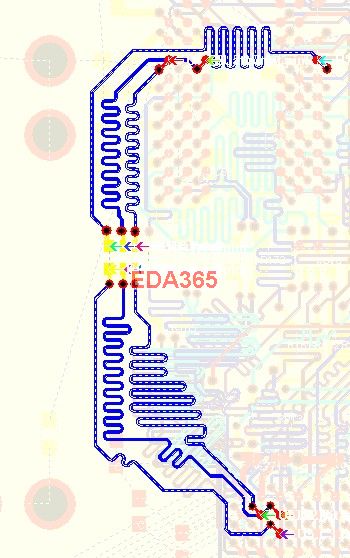

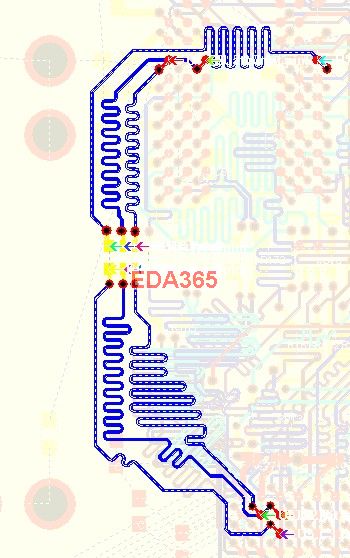

不知道放得对不对,旁边两根线作为干扰线,中间的那根作为被干扰线

仿真的结果如下图,感觉串扰是不是太小了?结果正确吗?哪位大虾给指点指点啊,谢谢啦

仿真的结果如下图,感觉串扰是不是太小了?结果正确吗?哪位大虾给指点指点啊,谢谢啦

这个不是最恶劣的,另外还有选择的码型

大哥,你是怎么同时选中三根线,并仿真的啊?我在boardsim中能同时选中一根线,但发现点了“Enable Crosstalk Simulation"与不点该按钮,出来的仿真图形一样的。我又将该按钮按下,并将驱动端保持低电平,但发现接收端一直是低电平,连个串扰都没有,你能不能帮我解释下为什么啊?多谢啦!

大哥,你是怎么同时选中三根线,并仿真的啊?我在boardsim中能同时选中一根线,但发现点了“Enable Crosstalk Simulation"与不点该按钮,出来的仿真图形一样的。我又将该按钮按下,并将驱动端保持低电平,但发现接收端一直是低电平,连个串扰都没有,你能不能帮我解释下为什么啊?多谢啦!

楼上的,串扰仿真是有线距要求的。建立模型,点击串扰后,就会出现串扰的仿真结果。

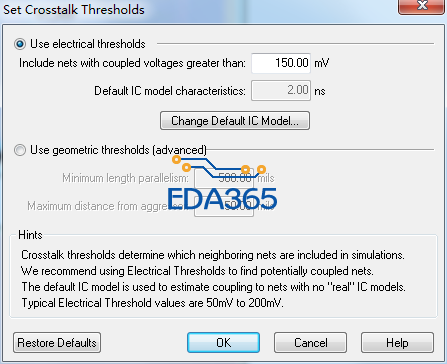

串扰要设置两种情况(选其一):

1.串扰电压(mV);

2.距离。