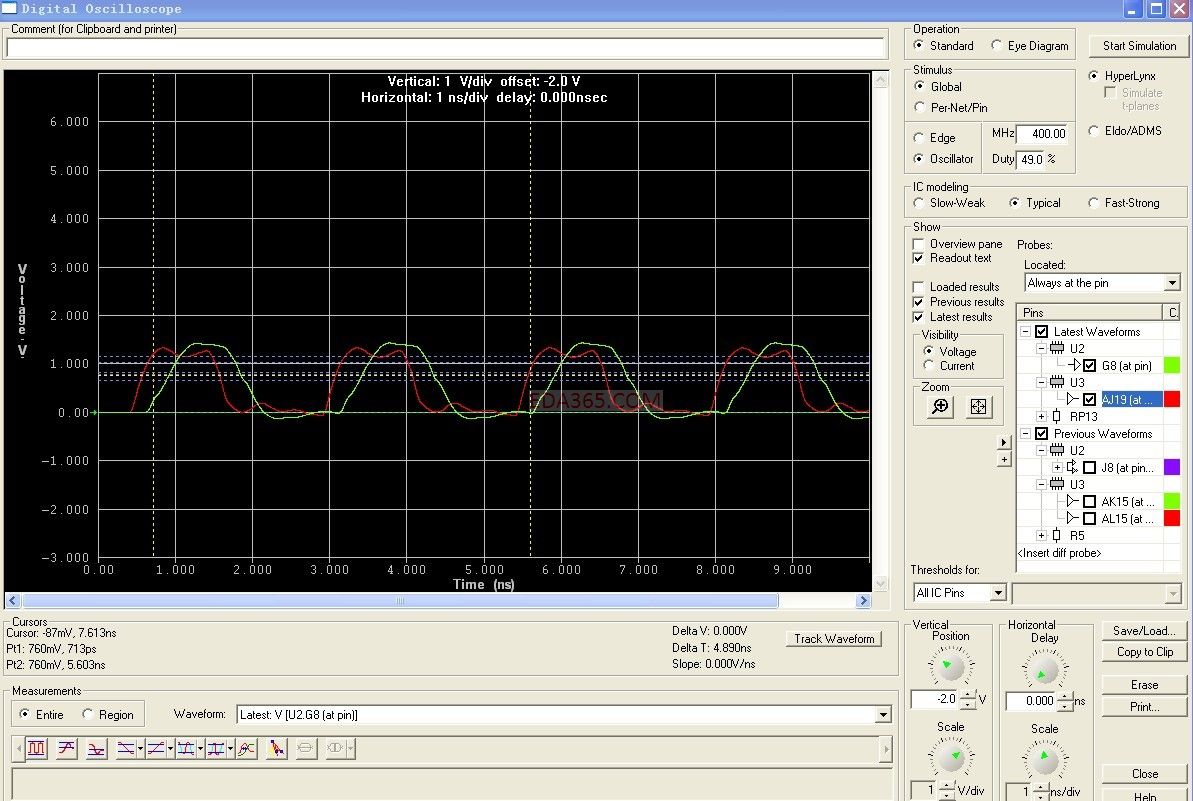

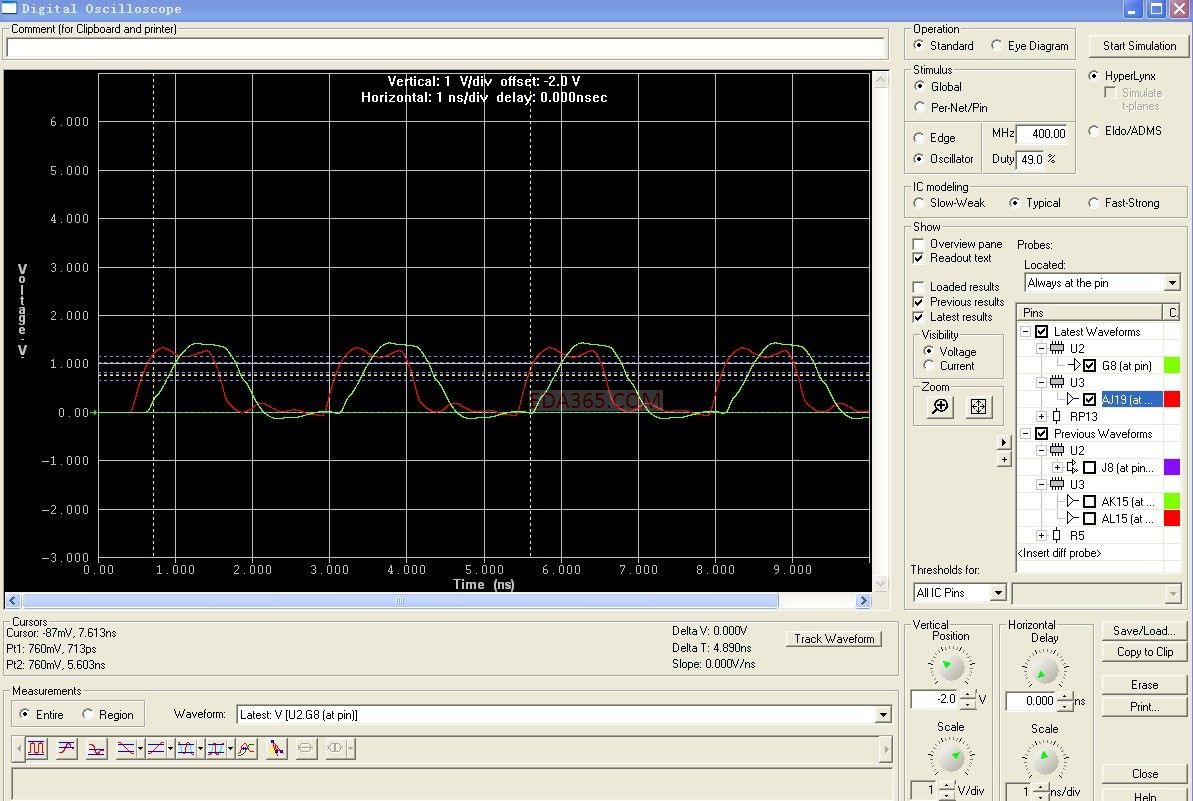

ddr2的数据线波形,高手指点

以下是我仿真出来的ddr2的其中一根数据线的波形,不知道有没有问题,怎么判断?希望高手指点一下。还有hyperlynx中能不能仿总线?

很不錯阿!

我估計線長約 2.5 inch

怎么判断出好坏?还有能不能同时仿真多根数据线?

怎么判断出好坏?

==> 參考時序的規格看容餘有多少,容餘越多越好。

还有能不能同时仿真多根数据线?

==> 我說過了,不行。

你的意思就是看建立时间和保持时间余量,但这必须是和时钟在一起比较才能看出来的吧!

同问,期待高手回答。

數據總線的眼圖,搭配 DQS (此圖未加入) 就可以判斷時序的容餘。

sixplorer支持总线仿真

老大,sixplorer是哪个公司的仿真软件?cadence?

提取拓扑到linesim,全部复制到一起就能仿真总线了

哦 其实我是想在boardsim中看

对照spec看余量

我也是这样做的。

频率应该设置为800M

你设置为400M 错了,除非你DDR2只跑400M

现在ddr2就跑200M的时钟,400M的数据率

hyperlynx中带有DDRx功能,可以进行总线仿真;也可以提取多根导线参数,进行仿真。

频率应该设置为800M$ E7 A0 ^6 z% \, Q, [4 x8 Z

你设置为400M 错了,除非你DDR2只跑400M

好像hyperlynx8才有吧!

学习

太厉害了!好想知道这个DDR2数据线波形是怎么仿真出来的?

仿真总线,还可以通过在boardsim中将走线按照s参数提取,然后在line-sim中调用s参数即可

比较过,差异较小

但是hyperlynx不便于进行时序仿真,比如仿真自动计算的min/max flight-time等均不正确,特别是max完全错误;此外因为没有flyby的波形,也不利于手工测量flytime的时间,只能大约评估,对于高速率,是无法保证精度的

另外,发现hyperlynx也不能进行总线的串扰后仿真分析

学习

敢问小编你这个DDR的控制器模型哪里找的

学习一下。

大神你分析的听不懂 做培训不我想学

DDR 不是集成了,用过DDR 向导,就可以对DDr 的读写时序仿真.

记号!留着用

我觉得仿总线就是看下串扰吧,就数据线来说小编的结果很不错了,数据线看电平,时钟线看边沿,数据线的电平时间窗口留的足够了,没有过冲和振铃,就行了啊。

对照手册或者JEDEC标准中的DC和AC特性图判断

学习了,记号

学习了

对照手册或者JEDEC标准中的DC和AC特性图判断!

学习了!