Hyperlynx DDRX仿真结果分析,跟大家探讨一下

时间:10-02

整理:3721RD

点击:

刚用Hyperlynx的DDRX仿了一下Memory,仿真的过程中DQ和DQS都过了,

但是Address和Control居然有几根信号没过,直接上图:

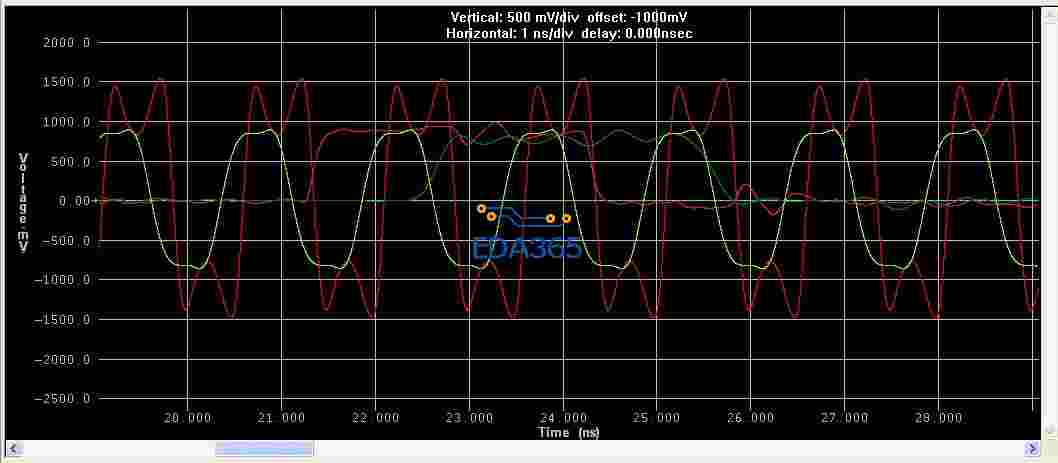

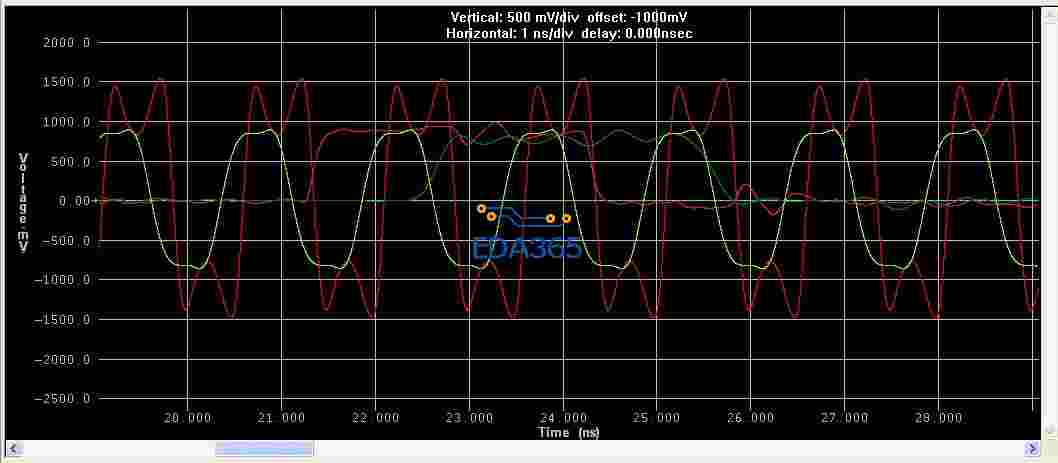

红色的线分别是Memory controller的clock和Address线。绿色的线是DRAM端的clock和address线。最后报错: MEM0_A0:Voltage of data waveform is in an undetermined logic state when its clock waveform crosses Vref! (neither low nor high)

不知道什么原因,感觉像是源端的clock信号有反射,是不是仿真的时候哪里设置有问题?

但是Address和Control居然有几根信号没过,直接上图:

红色的线分别是Memory controller的clock和Address线。绿色的线是DRAM端的clock和address线。最后报错: MEM0_A0:Voltage of data waveform is in an undetermined logic state when its clock waveform crosses Vref! (neither low nor high)

不知道什么原因,感觉像是源端的clock信号有反射,是不是仿真的时候哪里设置有问题?

哥们有没有这个功能的教程啊,我在做 不会用这个功能,谢谢了

这个是没有教程的,只能看help和别人发的例子,我现在也在摸索,等差不多了就写个东西出来,让大家都方便学一下,现在还不敢发,怕误人子弟,呵呵

呵呵 谢谢 我昨天摸索着用了一下 仿真出来了 好多单调性不过的啊 不知道影响大吗

没太明白你说的是什么意思,但是这个软件仿真的细节还是有很多的,把你的操作步骤啥的上图贴出来吧,要不没法帮你分析,不过的肯定是有原因的

结贴吧,捣鼓出来了,在Hyperlynx中需要设置PowerSupply,把这个VDD、VTT、Vref都给设置上信号就好些了。

这个VDD.VTT.VREF在哪设置啊

路过

在setup ----->power supplies中

你是前仿真还是后仿真呢?

后仿啊

为什么反向读数据报错:missing driver model?

给个读仿真的数据结果吧

LZ,请问DDR3读仿真的数据是怎样的呢?我刚自己摸索弄了一个DDR3 800的仿真结果,读的时序的建立保持时间和写的基本是一样的,这是怎么回事,显示的是PASS,可是不明白究竟是不是对的?按理读的TDQSQ应该小于200ps, Tqh应该大于950ps,可是仿真结果读写在一个数据表格里,反应的是Tds/Tdh,而且数量都是580到620ps,这个怎么理解呢,仿真结果自动将读操作DQS的相位作了1/2的BIT位偏移?

加QQ:64442092直接讨论

娄主强大啊,我还在摸索中

stevenzhao, 有其他联络方式么?请教一下DDRX的仿真问题

学习了,谢谢!

又細節的資料可以參考嗎

來學習看看