请教,一道面试硬件工程师的笔试题

时间:10-02

整理:3721RD

点击:

这是一道关于设计放大电路的笔试题,请教一下,谢谢!

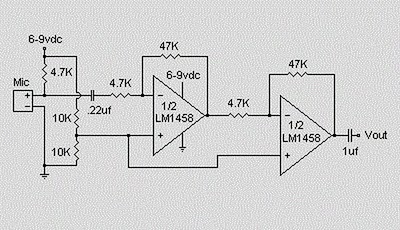

题目:MIC的输出属于差分输出,请用单电源供电的运放设计一个输出40dB的差分放大MIC信号的电路

题目:MIC的输出属于差分输出,请用单电源供电的运放设计一个输出40dB的差分放大MIC信号的电路

這樣應該算吧!

倍率就自已算囉~

40dB刚好是100倍,妥妥的!

小编大大,这个图中的MIC不是差分输出呢,运放放大电路这边也不是差分输入

学习学习

47K之间最好就要并一个151的电容比较好。

那個圖已經將參考地平移到 VCC/2,是不是再仿造一組就行?樓主可以思索一下。

兩組放大電路輸入當成差分訊號輸入,兩組放大電路輸出當成差分訊號輸出。

小编請教下,算增益時有時候看到公式是RF/R1,有時候是(RF+R1)/R1這電路是怎麼區分啊。之前學的基本都忘了,現在重新看的暈暈的。

不差不差,忘得真快。要搞懂,首先要忘掉你之前学的一堆名词,只需要记住两点:1,输入高阻=续断,运放两个输入脚电流为0;2,镜像特性=续短,运放两个角电压相等。然后用这两个特性基本就可以得到常用的一些运放电路输入输出关系了。不要记住什么RF/R1,(RF+R1)/R1,没意思,记住+理解刚才的两点这些图看一眼就知道是放大多少倍了。