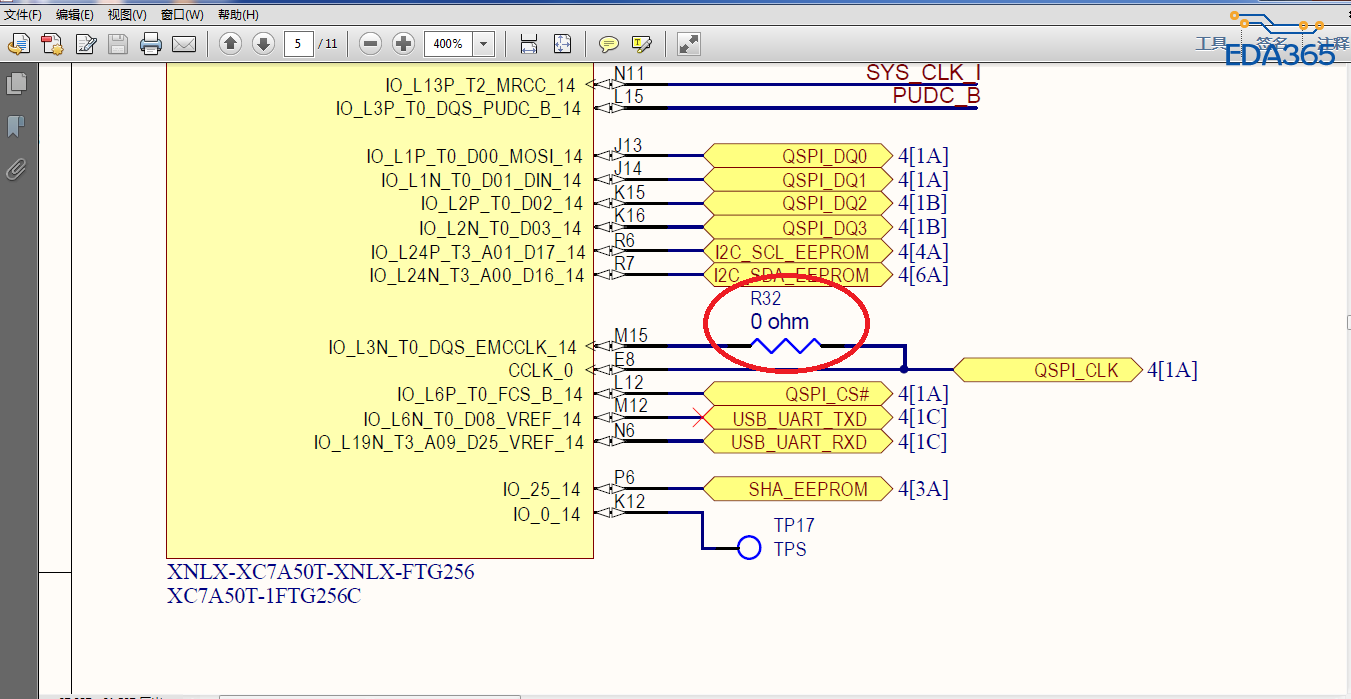

请问图中零欧姆电阻有什么作用?

时间:10-02

整理:3721RD

点击:

那个QSPI_CLK是接SPI NOR Flash的CLK.它已经接了E8脚的CCLK_0为什么还要用一个零欧电阻接M15脚? 这接的话,两个脚不是短路么?对时钟有什么作用?这个图是xilinx参考设计上的。

詳細的功能你要去看 FPGA 設計,我覺得 Xilinx 原本設計這個界面時,是可以作為 SPI Host 或 SPI Device。

- 當 FPGA 做為 SPI Host 時,接上 R32 可以提供一個 Clock 給 Device。

- 當 FPGA 做為 SPI Device 時,拿掉 R32 可以接受來自另一個 Host 的 Clock。

基本上 M5 的時鐘訊號,可以在 FPGA 內部繞到 E8 的管腳出來,並且做成雙向的訊號。但會犧牲 FPGA 中的一些 Gate Count 和 Routing Resource,並且增加少許的延遲(Delay)。Xilinx 可能不想犧牲這些代價來做這件事,畢竟也只是開發板吧?

類似這樣的 FPGA 設計我曾經看過,但實際上你還是得查看一下 FPGA 的 HDL 原始碼確認。

帮顶

帮顶

帮顶