求大于1S延时电路~最低成本方案!急

时间:10-02

整理:3721RD

点击:

芯片的Key pin 在1S内检测到两次大于1.5ms 的下降沿就会触发内部某一功能,当进入这个功能后,芯片没有办法在输出空载的时候实现自动关机,客户不需要此功能,但是芯片没有办法关掉,所以只能外加电路屏蔽这个1S内的两次大于1.5ms低电平(并且需要将这两个低电平专为单次大于1.5ms的),因为项目时间紧迫,在此寻求解决方法.感谢不已!

做个RC电路就可以实现了。

不大好做.

RC电路有什么不好做的,高中就学过的电路吧

翻翻大学课本,然后好好计算一下RC

RC就电阻和电容当然简单啊,是我的标题没写好,你们看看具体的描述吧。醉了.

你们搞些能有用的行吗?仔细看看描述吧!

这个信号是如何驱动的?是否可以在驱动端想办法?

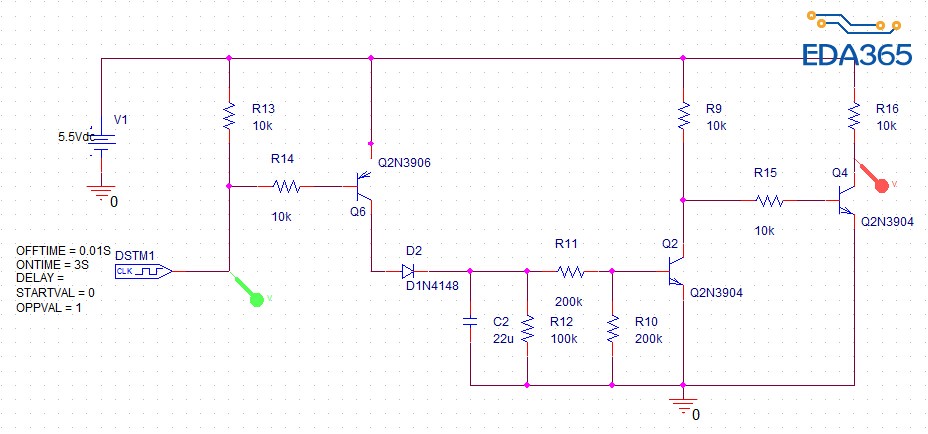

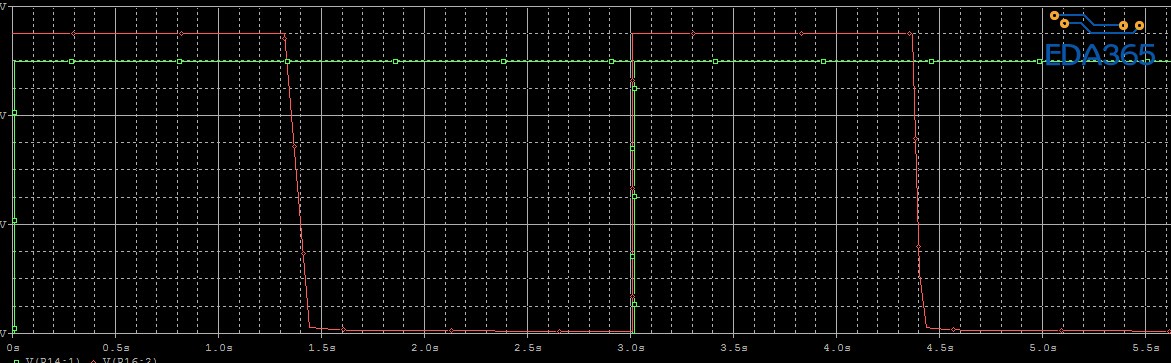

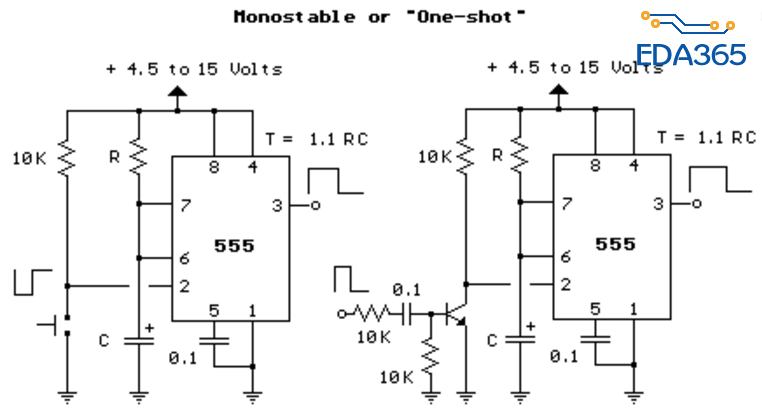

僅供參考

阅读权限: 9

你这个是因为KEY信号抖动造成的吧?如果是,RC+三极管可以改善

谢谢啦!哈哈

这个似乎可以