LDO控制脚的时间计算

时间:10-02

整理:3721RD

点击:

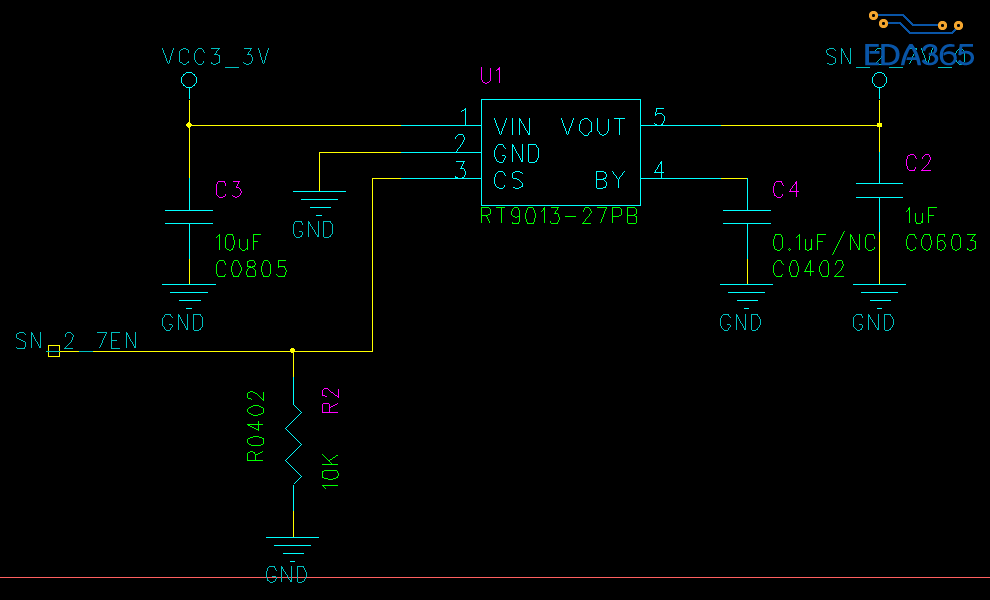

如图,第三脚的控制脚是接到主控的IO口的,主控输出3.3V来控制。当断电后,3.3V通过10K电阻放电。多久的时间,可以把3.3V的电放完?怎么计算?

IO口里面一般是开关,当断电后,开关就断开了,开关后面没有能储电的器件,所以基本不存在你说的电阻对地放电时间的计算....

这个是放电的么?我记得是稳定控制信号的,哪个大婶详细解释下,搂住把datasheet发出来。麻烦了

放电?!

如何计算?

基本上等于你的电源的放电时间。

没法计算吗?如果没有这个10K电阻,断电后不会马上变成0V吧。

因为你是IO口输出高电平控制这个,所以不清楚内部是如何的。

猜测你的输出是推挽的,所以加了这个10K用于开机的时候,对于电源IC的CS是确定的下拉电平。

rc才会延时

电阻放电?计算时间?

10K下拉是为了确保上电到控制IO口初始化成功之前的低点平,如果关闭使能,LDO输出下降的慢是因为输出端消耗电容里的残留电荷太慢

元件、IC、走线等寄生电容加起来的C再与这个10K去计算吧。

这个貌似和你的电源系统的容性负载有关系。