求助DDR3芯片的一些问题

时间:10-02

整理:3721RD

点击:

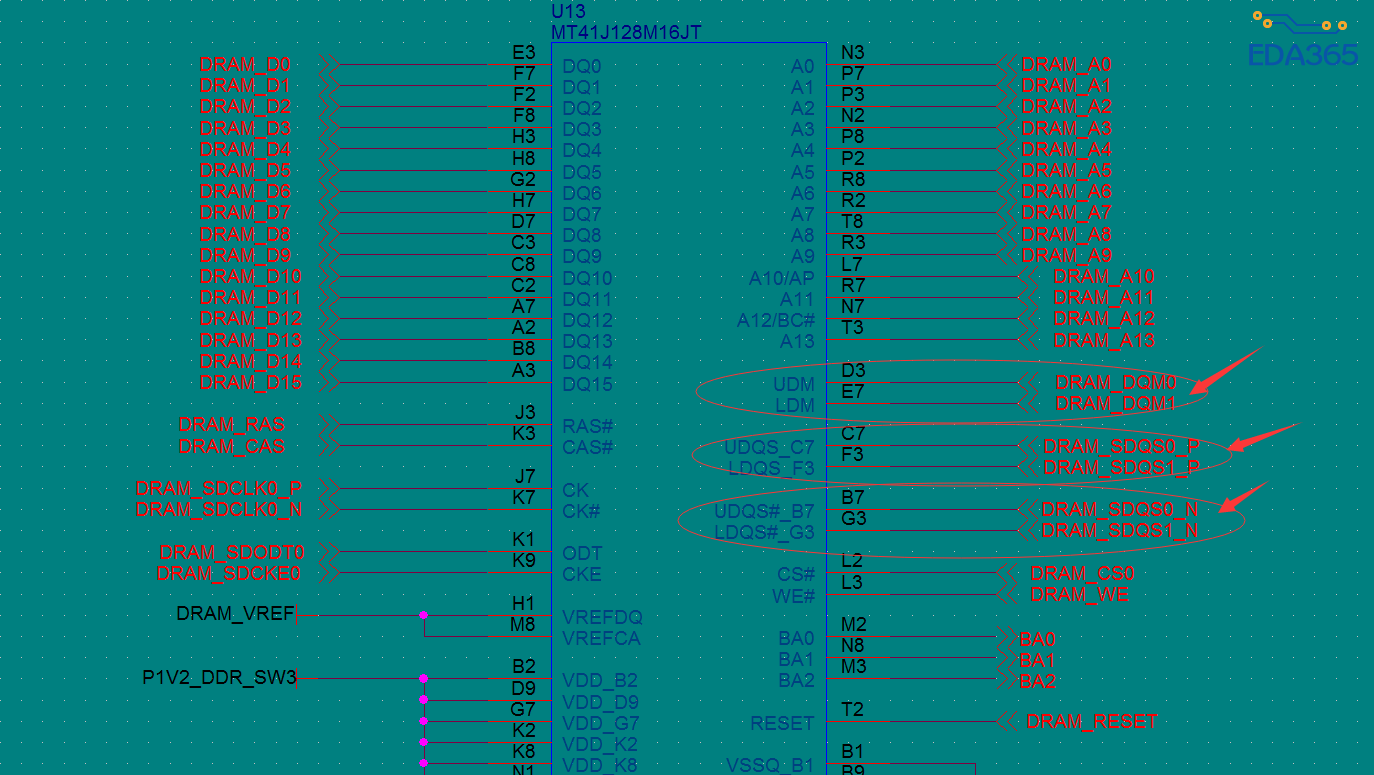

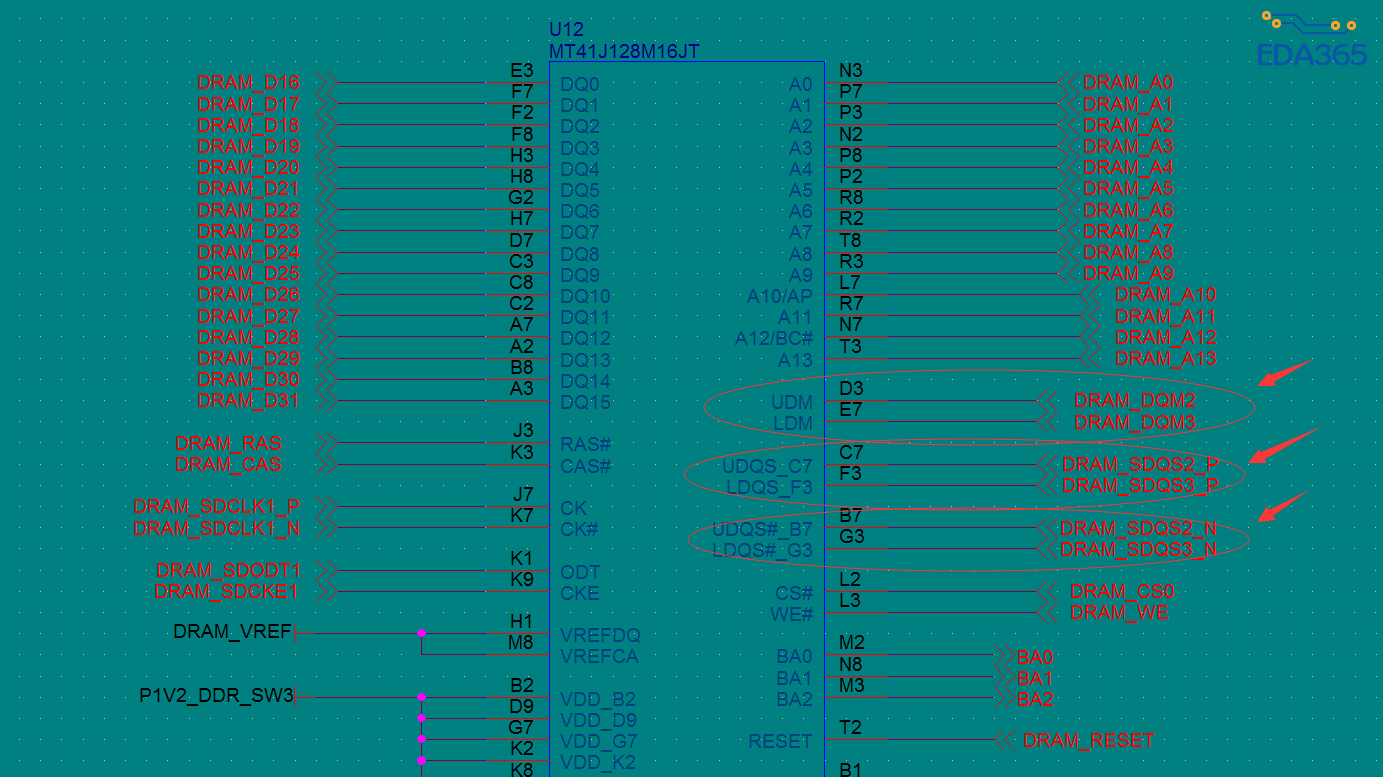

各位大神下午好,小弟又来求指导了。最近在研究DDR3相关的一些事情,马上会上马一个DDR3的项目,有一些补清楚的事情还请各位大神指导指导。小弟在下面的两幅图中标记处了一些不太明白的地方,不知道小弟这么连接对不对。还有就是DDR3芯片每一片都是16bit的,那么如果是32bit的,按照小弟这种连接方式对不对,是不是就组成了32bit的内存。是不是就会变成128M*32呢?

另外,最近看了很多关于DDR3芯片的布线说明,一定要求每一个分组都是要再一个平面上,但是看主芯片推荐手册上面的布线图发现DQS这种差分线都布在了表面,完全没有跟数据线和控制线一个层面,这又是为什么呢?是为了阻抗匹配么?

另外,最近看了很多关于DDR3芯片的布线说明,一定要求每一个分组都是要再一个平面上,但是看主芯片推荐手册上面的布线图发现DQS这种差分线都布在了表面,完全没有跟数据线和控制线一个层面,这又是为什么呢?是为了阻抗匹配么?

DDR3芯片1

DDR3芯片2

数据线拼接,地址线连在一起(不分叉走线)。走线的时候DQ0-7 DQSP0 DQSN0成一组,等长处理。地址线和控制线设成一组,登场处理。

大神,这么早!

感谢大神的回复,分组方面我大概了解,现在我比较疑惑的一点是在用DR3芯片组成32位的系统的时候,是不是按照我这种接法,还有就是CLK和ODT,是接通一个CLK跟ODT还是说分开接CLK0,CLK1这种呢?

CK ODT CKE 连到一起。你的好像错了。

感谢回复,是的,我也发现了这个问题,也是看参考图的时候一个一个数出来的时候发现出错了,还有就是我的大小端的DQS也弄反了,应该是DQS1接高字节,DQS0接底字节。不知道我说的对不对、

没错 另外要考虑预留终端匹配电阻和VTT。

这两个是接在哪里的啊?有没有示意图能发我看一下啊。谢谢了。

公司发不了图;

匹配电阻是放在控制信号和地址信号上的,一般51R,VTT是上啦电源,要有一个专用的VTT电源芯片,可以提供灌电流和拉电流,推荐TI的TPS51200,自己看手册。

好的,非常感谢!

CLK0 和CLK1是不是分开接要看主芯片的设计方案 DATAsheet上面一般都写得很清楚。