请教一个关于过孔与高速差分线之间的问题,坐等大牛!

时间:10-02

整理:3721RD

点击:

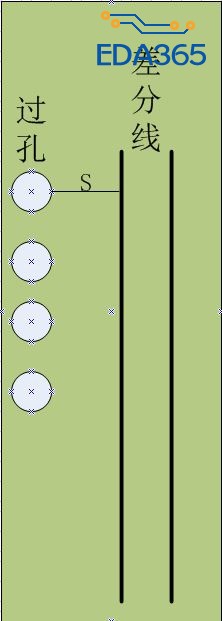

1、过孔离高速差分线的距离当然是越远越好啊,那到底过孔离高速差分信号的最小距离是多少呢?

2、如下图中纵向上过孔的个数最多可以有多少个,即高速差分线旁边最多可以有多少个过孔?

3、低速过孔是否对高速差分线没有影响,多高的速率可以认为没有影响?

请大家各抒己见,谢谢!

2、如下图中纵向上过孔的个数最多可以有多少个,即高速差分线旁边最多可以有多少个过孔?

3、低速过孔是否对高速差分线没有影响,多高的速率可以认为没有影响?

请大家各抒己见,谢谢!

手機PCB上,差分線只需要上下左右包地即可,不太關注這些via。我認為差分線本身就是抗干擾設計,沒必要這麼刻意去保護。包地足够了

上下左右包地,当然不用在意过孔啦!因为信号线和过孔之间用地给隔开啦!

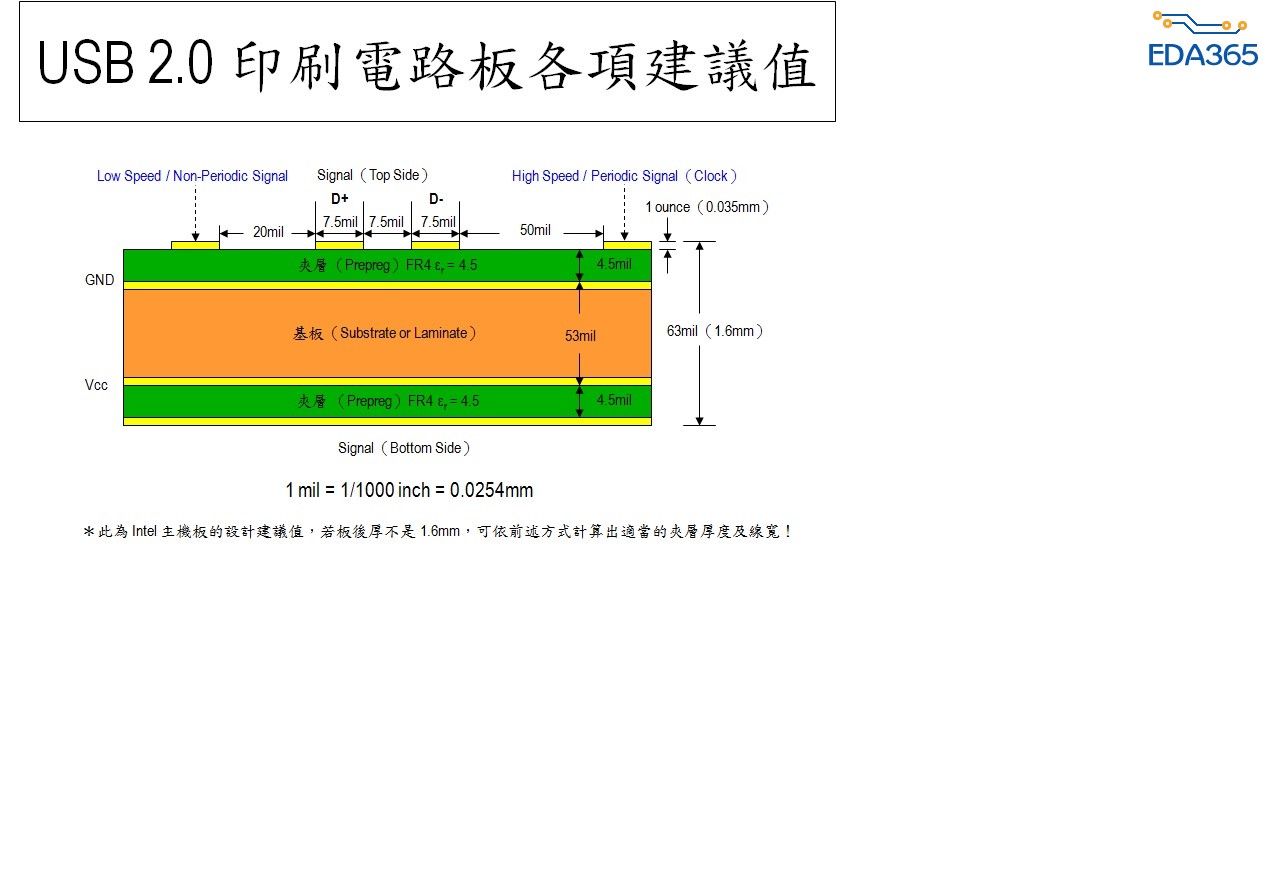

過孔如果指的是其它訊號,一般同高速訊號建議遵守 3L 規則(3L Rule)。

這樣建議的常見於 USB 或 DDR 的應用上。

來個英特兒(Intel)的 USB 建議!

3L规则具体指什么?

借樓主的地盤,也順便諮詢一下:

我這邊要求Clock遠離其他信號線20mil,

Clock與其他走線、焊盤等,Layout直接添加rule,可以滿足20mil的要求。

但是這個規則里,不包含過孔。附圖里,過孔與clock就只有6.66mil。

還有,為生產需要,95%的網絡需要加測點(附圖黃色高亮網絡),因空間限制,同樣不在這個20mil的規則里。

那問題來了,過孔不是會影響信號質量嗎,難道過孔和測點難道是可以排除在外的嗎?

建议是3W以上

你这个几个问题其实就是问的一个问题,高速干扰,但是这些都有一个前提,需要考虑的你成本。如果只是理论研究没有实际意义。个人认为在不太KILL成本的时候,高速线离所有线号线5W以上,并且都做包地处理。