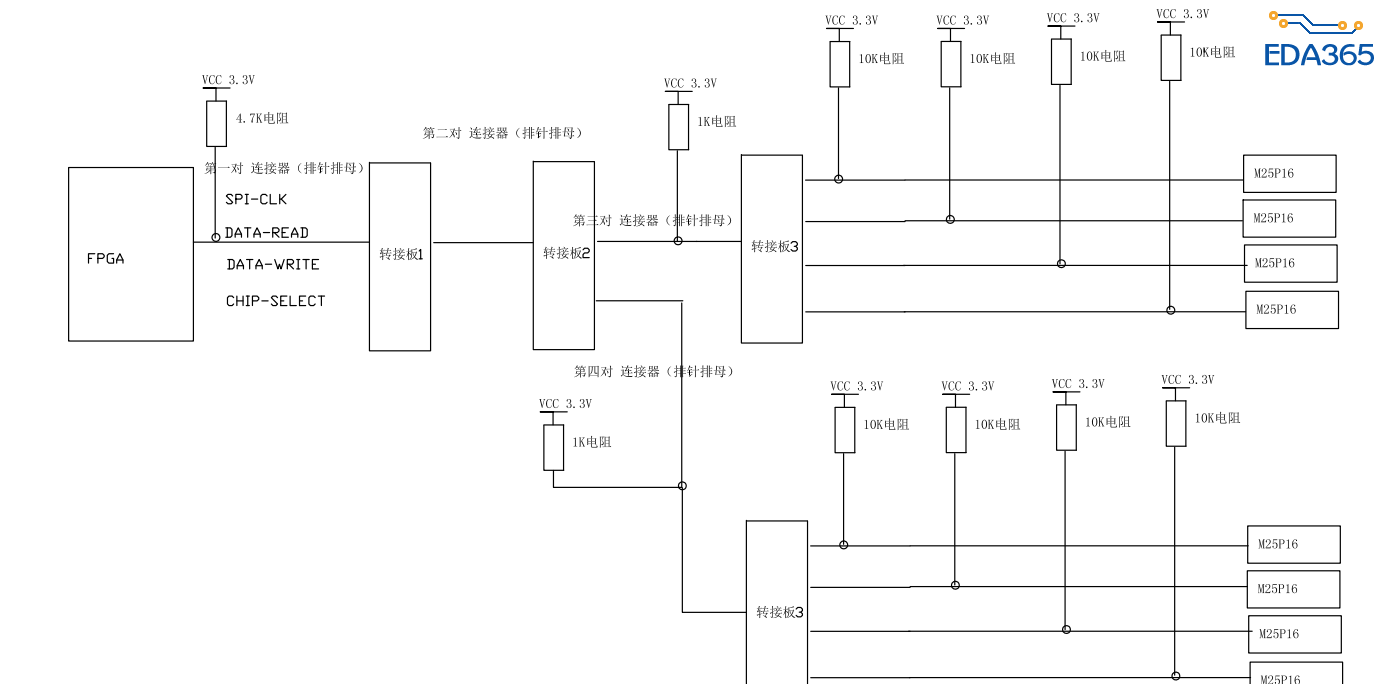

求大神-SPI存储芯片数据读取错误问题

目前,读写都没有问题,但是在读取数据的时候会随机出错,并表现在终端上,每次复位,发生错误的地方都不相同。所以应确定数据是在读取的时候错误,而不应实在写入的时候错误。这样的随机现象也很难通过抓取波形发现。那么发生错误的最大原因是什么呢?

10K上拉,太大了吧,可以换小点试试

数据输出这个信号 是低有效的。所以加更小的拉阻,有可能导致信号变换到低状态的时候,上拉的电流大大延缓他的下降时间。这是我现在怀疑的地方!

看整条线上的拉阻,并联起来,实际阻值只有300多R。不知道是否可以这样计算,这是我不确定的地方

补充描述:FPGA到M25P16 整个过程中,data-read这条线没有任何器件整形,完全以分支的形式分别连接8个从属芯片

确实是按照并联算呢,上拉的太多了,在驱动端上拉就好了,上拉小点,增加驱动能力,看下芯片手册,只要电流在芯片输入范围内就好了。

另外不知道你的SPI总线速率多少------简单的经验法则估计传输线损耗,即FR4板上线长(in)大于50×上升边(ns)时,损耗的影响将起着重要的作用。

支持5楼,以前做过I2C的1拖5,长度差不多。只在驱动端拉,末端预留,没有什么问题。

我觉得你先看看波形有没有大的异常;或者这种拓扑还可以考虑用cadence仿真下,sigxplrer简单仿一下

就是波形看不出异常

通过串行时钟触发25P16的数据输出信号,通过逻辑分析仪查看信号时序,都找不出明确的原因。所以才说这样随机的问题,很难解决。需要大量的测试数据可能才能找出来。

先看简单地片选时序会不会出错

这种互联那么多的,波形应该很难看吧。先把波形整整。

从你的图上看是1拖8哦,这样数据线上的负载肯定是很重的。

可以先用示波器在FPGA端,看下SCLK和MISO的时序是否有风险。

尝试将FPGA和NOR的驱动能力都调到最大;SPI频率降低到1M以下;或者将所挂的器件数减少;

看下是否还有出错?

目前的电路中。MOSI,SPI-CLK 也是一带8,中间有添加245整形,MISO因为器件数量的原因,省略了整形这一步骤,是否跟这个有关系?

时序的波形明天上图!