遇到这样的面试问题大家怎么看?请教各位大虾,各位版主大神

时间:10-02

整理:3721RD

点击:

前不久,本人去参加了几个面试,遇到了个别面试官问这样的问题:

1、信号在PCB板上的传输速度是多少?

小编愚昧,记不住,只能大概记得是光速一半(以前看信号完整性时有遇到过)。貌似这样的回答面试官很不满意;

2、pcie总线使用的AC耦合电容是多少?

小编答:2.0用100nf 3.0用220nf 根据pcie协议里面写的,是个范围值。以上是常用值。

面试官追问:那为什么这两个要选100nf 和220nf,原理是什么?

小编知识有限,不知道了。我只知道2.0的pcie电容范围大概是75--265nf,3.0PCIE是180nf--到具体多少忘了 ,记不住。

等等这些类似的问题挺多,搞得在下感觉自己很渺小。

在下工作有3年时间了,做了不少项目,确实很少在工程上去考虑以上这些问题。或许是我知识面太窄了。特来请教大神和斑竹们,给点意见,我想好好学硬件,有兴趣。

1、信号在PCB板上的传输速度是多少?

小编愚昧,记不住,只能大概记得是光速一半(以前看信号完整性时有遇到过)。貌似这样的回答面试官很不满意;

2、pcie总线使用的AC耦合电容是多少?

小编答:2.0用100nf 3.0用220nf 根据pcie协议里面写的,是个范围值。以上是常用值。

面试官追问:那为什么这两个要选100nf 和220nf,原理是什么?

小编知识有限,不知道了。我只知道2.0的pcie电容范围大概是75--265nf,3.0PCIE是180nf--到具体多少忘了 ,记不住。

等等这些类似的问题挺多,搞得在下感觉自己很渺小。

在下工作有3年时间了,做了不少项目,确实很少在工程上去考虑以上这些问题。或许是我知识面太窄了。特来请教大神和斑竹们,给点意见,我想好好学硬件,有兴趣。

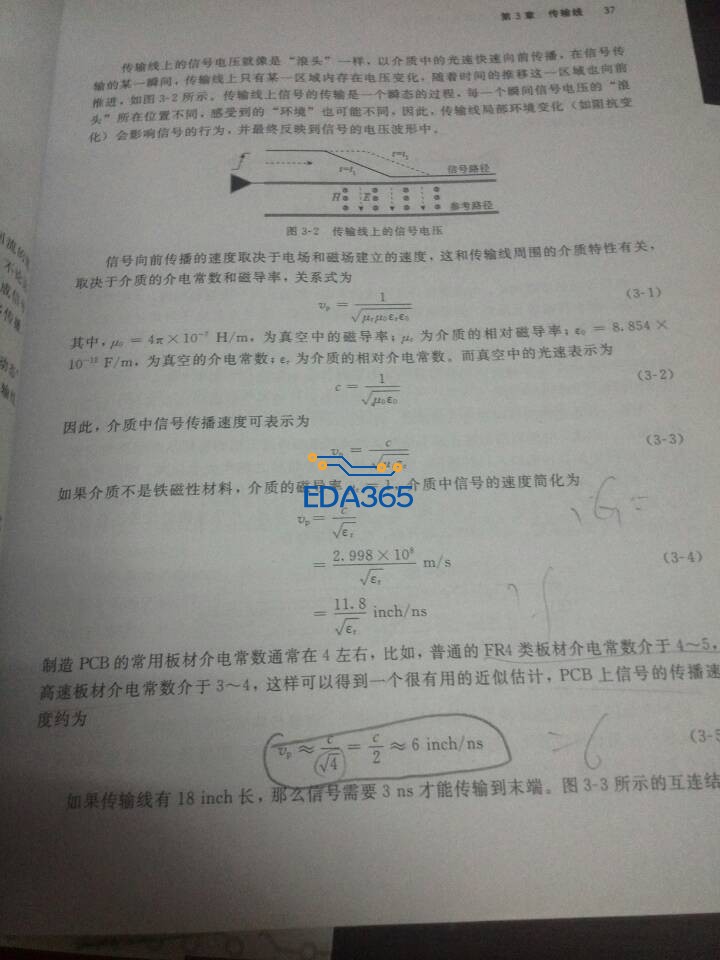

第一个问题 我附了一张图可以解释,来自于博士的信号完整性的书;

第二个问题没太多接触

对的,是这个公式,只不过平时基本不用这些,时间一长就记不清了。光速一半

这个面试官提的问题本身就不清晰:信号在PCB线路上面的传输速度与传输环境有很大关系,例如,介质的介电常数,线宽,传输线位置等,有数据表明,同样频率的信号在微带线上面传输速度略快于带状线。

是的 和介电常数 磁导率是有关系的吧

FR-4板材,内层180ps/INCH,外层140ps/inch,做粗劣评估用。

第二问题跟速率有关,应该越快电容要越大,有公式的。电容小会丢码,以仿真为准。

这样的啊,本人不是很了解哦。只是在协议里面看到过取值范围。

那我不明白 为什么sata或者sas这类高速信号用的是10nf的呢,sata3.0,sas3.0是6Gb的信号,比PCIE2.0速率高,为什么sata、sas用的电容(10nf)比pcie用的小呢?难道除了和频率有关,还与别的有关吗?求指教

有计算公式忘了,你自己可以百度找找。

高深莫测

我怎麼感覺樓主一天到晚都在面試?

這類似事件不是去年才發生過?