关于DVI编码芯片SiI1162的输入时钟

时间:10-02

整理:3721RD

点击:

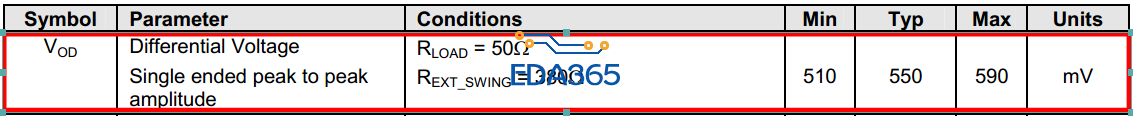

在使用DVI编码芯片SiI1162时钟时发其时钟有两种选项,单端输入以及差分输入两种选项,本来我只使用单端输入时钟信号,问题是差分输入是LVDS那种差分信号还是其他什么形式的差分信号,亦或只是相位相差180°即可?看了很多与它相关的芯片,也没有详细的说明,盼大侠详解。

Voltage level input on VREF sets the SiI 1162 in High Swing or Low Swing Mode. In High Swing Mode, only single clock (IDCK+) dual edge is proce ssed. IDCK- is ignored in High Swing Mode. In Low Swing Mode DVO mode, IDCK+ differential clock dual edge is processed.

VREF=0.75 CTL=High swing Mode DVO mode

VREF=VDDQ/2 Low swing Mode

VREF=3.3 High swing Mode

之后具体差分信号的幅度 datasheet中确实没有提及,我的不得而知。不过你可以问问他们的FAE。