帮忙分析下这个电路

时间:10-02

整理:3721RD

点击:

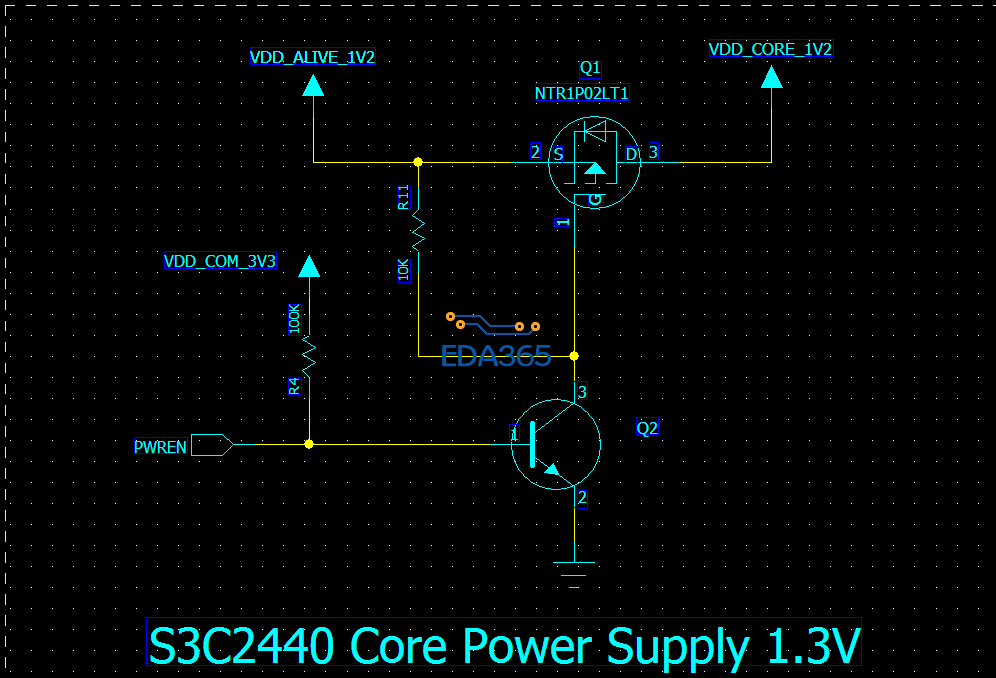

帅哥美女们,谁能帮我看看这个电路什么原理啊,谢谢了

就是PWREN拉低时,Q2截止,Q1截止。PWREN拉高或者高阻,Q2导通,Q1导通。

非常典型的信号控制大电流开关:power_en高,Q2导通,PMOS管通,VDD_core_1v2上电;power_en低,Q2截止,PMOS截止,VDD_core_1v2下电

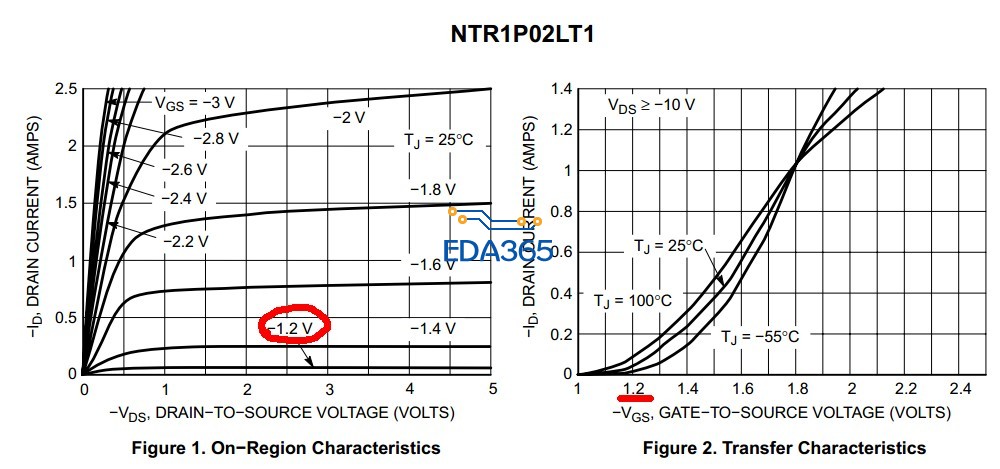

在VGS只有1.2V的情况下,MOS管的电流Id让人担忧....

四樓所言極是!

power_en为高时 G极电压应该不会为0,不知道MOS管是否能导通

追问一下:R11=10K的电阻是起什么作用?

核心电压 电流大 这个管能行?

R11应该用100K好一些,R4应该要下拉

你这个电路本身可能会有问题,Q2应该改用N—MOS管,否则Q2基级为高时Q1的G级仍然有2.6V左右的电压,Q1不会导通的

这个电路本身可能会有问题,Q2应该改用N—MOS管,否则Q2基级为高时Q1的G级仍然有2.6V左右的电压,Q1不会导通的.你们觉得呢?

这个电路本身可能会有问题,Q2应该改用N—MOS管,否则Q2基级为高时Q1的G级仍然有2.6V左右的电压,无论PWREN是高是低,Q1都不会导通的.所以1.2V根本过不来,你们觉得呢?

有写地方不能用这电路