请问下这种嗡鸣器设计的上拉电阻的作用是什么?

时间:10-02

整理:3721RD

点击:

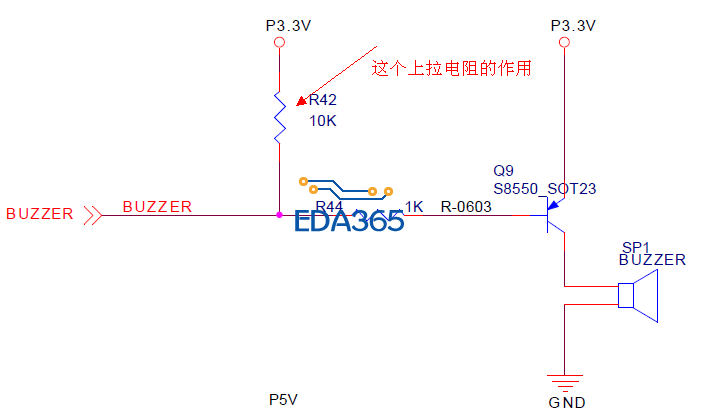

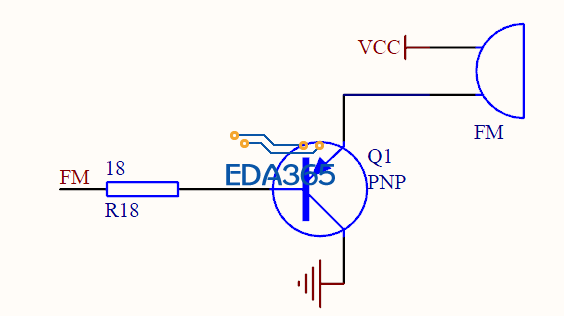

请问下这种嗡鸣器设计的上拉电阻的作用是什么? 随便解释下它的工作原理。 ,,以及这两种设计方法的区别与共同点

设计一

设计二

我觉得有这么个作用:当IC口状态不明的时候,加上上拉就能保证蜂鸣器不会响。只有当IO口被拉低的时候,蜂鸣器才会鸣响。特别是处于MCU或者CPU刚开机的时候。

应该是这样的,,谢谢了哈,,当为低电平时,发射极e和基极b的PN结导通,,从而集电极c和发射极e导通,即蜂鸣器所在回路导通就发出声音了。

第一个上拉啊,第二个应该换NPN管子才是。

第一个电路:现在的处理器等上电状态基本多是输入高阻状态。上拉固定了高电平,上电的时候蜂鸣器不会叫一下。

为什么第二个得是NPN管子才可以呢? 要不你解释下这工作原理吧。 我觉得这两个设计原理是一样的吧,,只是第一种加了个上拉电阻,,第一种是用在FPGA上的,,第二种是用在单片机上的,,,两种都可以用哟

第一个电路如果换成NPN管子的话,那这个管子的位置就要调换下了。另外,我倒是觉得第二个电路的管子可以换成NPN,用PNP管应该也能用,但是看着好奇怪啊,

如果不加上拉,下载程序的时候蜂鸣器会响