求助:大电流DC-DC模块+模拟+数字的PCB板子该如何布局?

由于DC-DC一般波纹较大,而模拟又比较敏感,所以拟采用下面的布局,不知道是否合理?大家帮忙看看!谢谢了!

模拟和CPU换下 模拟和其他所有数字部分隔开。

为啥模拟和MCU换下?这样不是模拟和DCDC更近了吗?会不会受到影响?

另外,模拟部分主要是外界电缆输入的微小信号调理,然后再进入MCU,换一下是不是不太好啊?

这样啊 理解错了。

这样做吧。

第一,采用独立的DC-DC或者LDO给你所谓的模拟部分供电,这部分电路放置在整个布局的靠左上部分。

第二,采用独立的DC-DC或者LDO给你所谓的数字部分供电,这部分电路放置在整个布局的右下部分。

模拟和数字电源采用独立的电源层,做完整的电源分割。

第三,所谓的模拟部分紧挨着模拟电源放置,位于整个布局的中上部分。

第四,所谓的数字部分紧挨着数字电源放置,位于整个布局的中下部分。

第五,所谓的CPU,基本都属于数字信号输入,除了音频,视频等特殊信号,需要特别处理,其他的都可尽量至于整个布局的中间部分,距离模拟部分稍远即可。

最后一点,你这个是什么板子,一般的板子也不要太严格要求,我们公司的产品都没有严格的电源层的。很多板子能有完整的地层就不错了。不过对于高速电路板来说,或者说模拟混合电路板来说,越是考虑周全,越能够获得好的效果,付出和回报基本成线性。

一般是完整地,另外模拟和数字要单点接地比较好,如楼上所说,分别采用两个电源比较好,数字走线不要经过模拟部分。采用电源分割。

一个测试设备的板子,该测试设备工作环境恶劣,同时需要外接高精度的各种传感器(模拟接口的)。所以要尽量避免受到干扰。并且还要通过emc的B级测试

再请教下,板子上的模拟接口要不要接下TVS或保护二极管(如BAT54S)?如果要接的话串联的电阻不是会对输入模拟产生影响么?

TVS管是瞬态电压抑制器(Transient Voltage Suppressor)的简称。它的特点是:响应速度特别快(为ns级);耐浪涌冲击能力较放电管和压敏电阻差,其10/1000μs波脉冲功率从400W~30KW,脉冲峰值电流从0.52A~544A;击穿电压有从6.8V~550V的系列值,便于各种不同电压的电路使用。

稍微说一句,TVS管是并联在输入接口上的吧,为什么说是串联的电阻呢?对模拟信号的影响的话,第一查看你信号的频率,选择相应寄生电容的TVS管。

至于你是否选择加TVS管的话,那你需要看你用在哪里了。

如果要我来设计的话,我会将模拟信号进来系统以后。第一步,进行阻抗匹配。(如果不需要可以省略) 第二步,采用一个巴伦,将模拟单端信号变成差分信号。第三步,采用差分的运放对信号进行放大。第四步,采用差分采样AD对差分信号进行采样。如果有比较 可以在前端加上滤波器。

如果你不使用巴伦的话,貌似TVS管是有必要进行加上了。

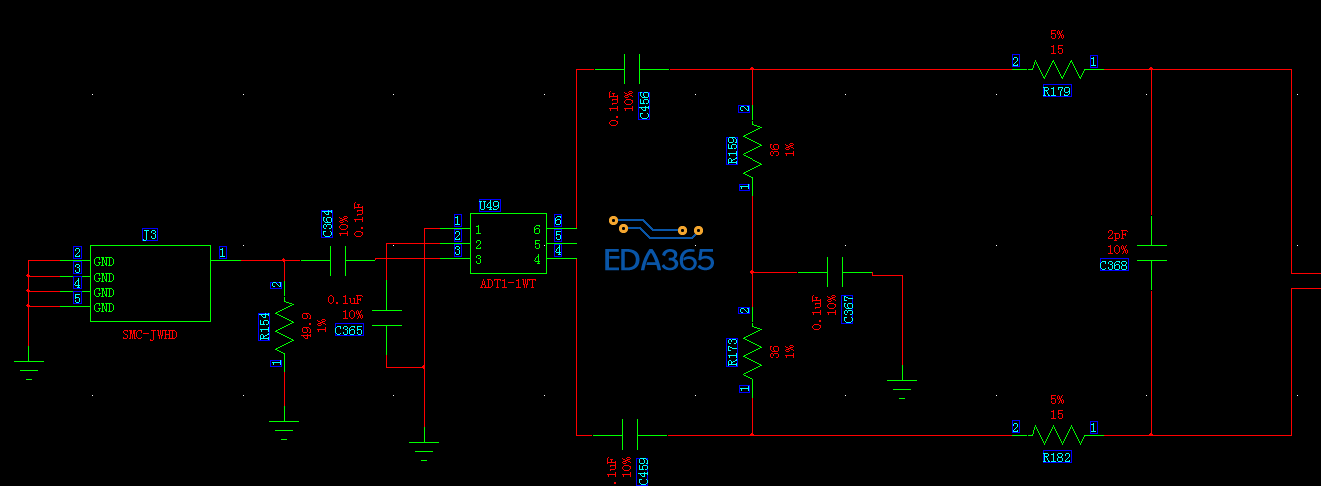

感谢您的回复。我的系统大概是这个样子。

如果加了BAT54S的话,假如当前输入信号为10v,由于BAT54S的原因,信号会被钳制在5v,那么多余的5v去哪了呢?是不是要在信号输入的线路上串个电阻呢?如果串了这个电阻,那么如果当前信号只有3V,那么这个串的电阻不会对信号影响吗?

唉。没搞过模电,有点菜。

我有点疑问哈。你为什么选择BAT54S呢?为什么没有选择其他管子?你这里加一个TVS管是用来防止大电压进来吧?我觉得要加一个BAT54A就好了。

如果你加一个BAT54A,也会存在限幅的问题么?

其实我也是菜鸟,很多东西都是说不清楚。你可以参考一下别人的设计,比如可以参考ADI公司的高速AD采样。

这个是我以前画的AD采样的电路,你可以看看。

布局还行,只是最好将模拟和数字的间距拉大,将模拟部分重要线包地。

做是做过好多,一时也很难说清楚。

能给个例子吗?特别是输入口接TVS那块,始终弄不明白。