求助!原来6层的PCB精简层4层,无头绪啊!

时间:10-02

整理:3721RD

点击:

情况是这样的:

产品是视频监控的DVR板子,使用的是海思HI3531+公司自己开发的DSP芯片。

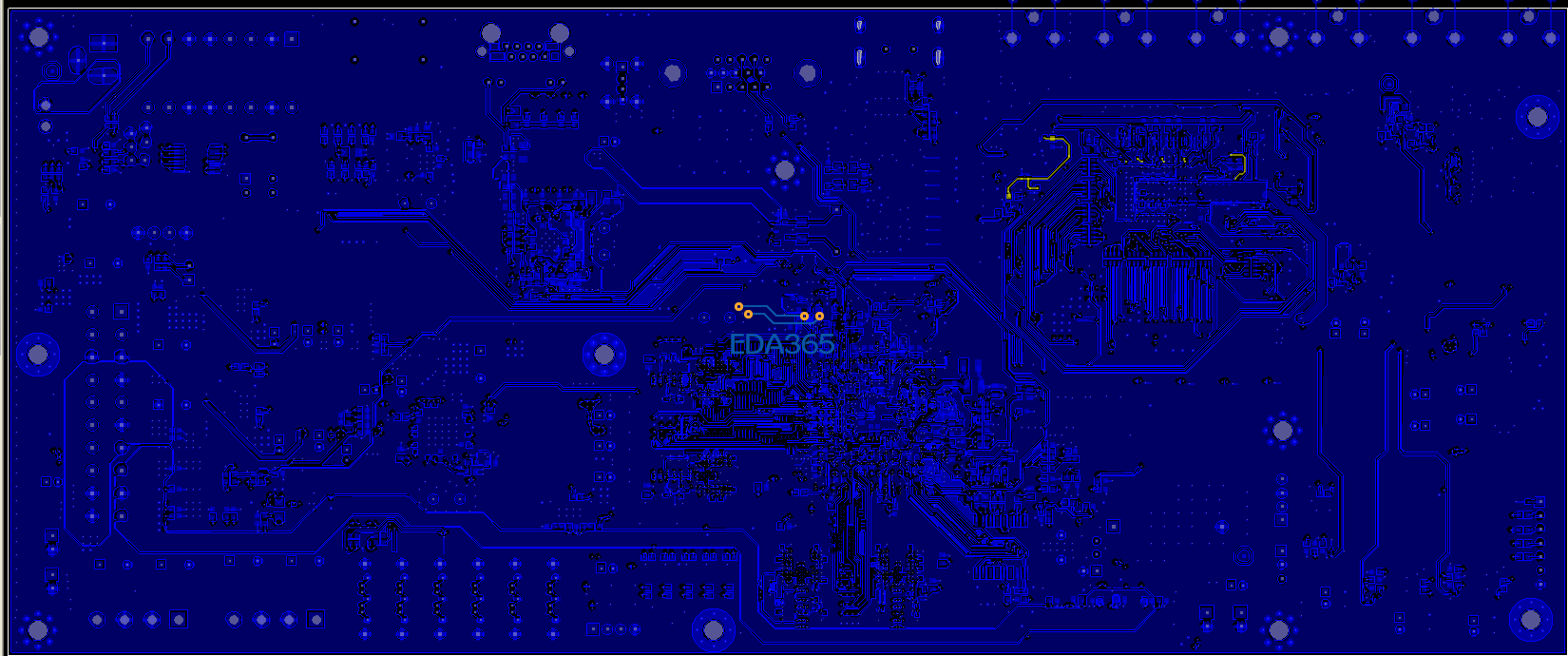

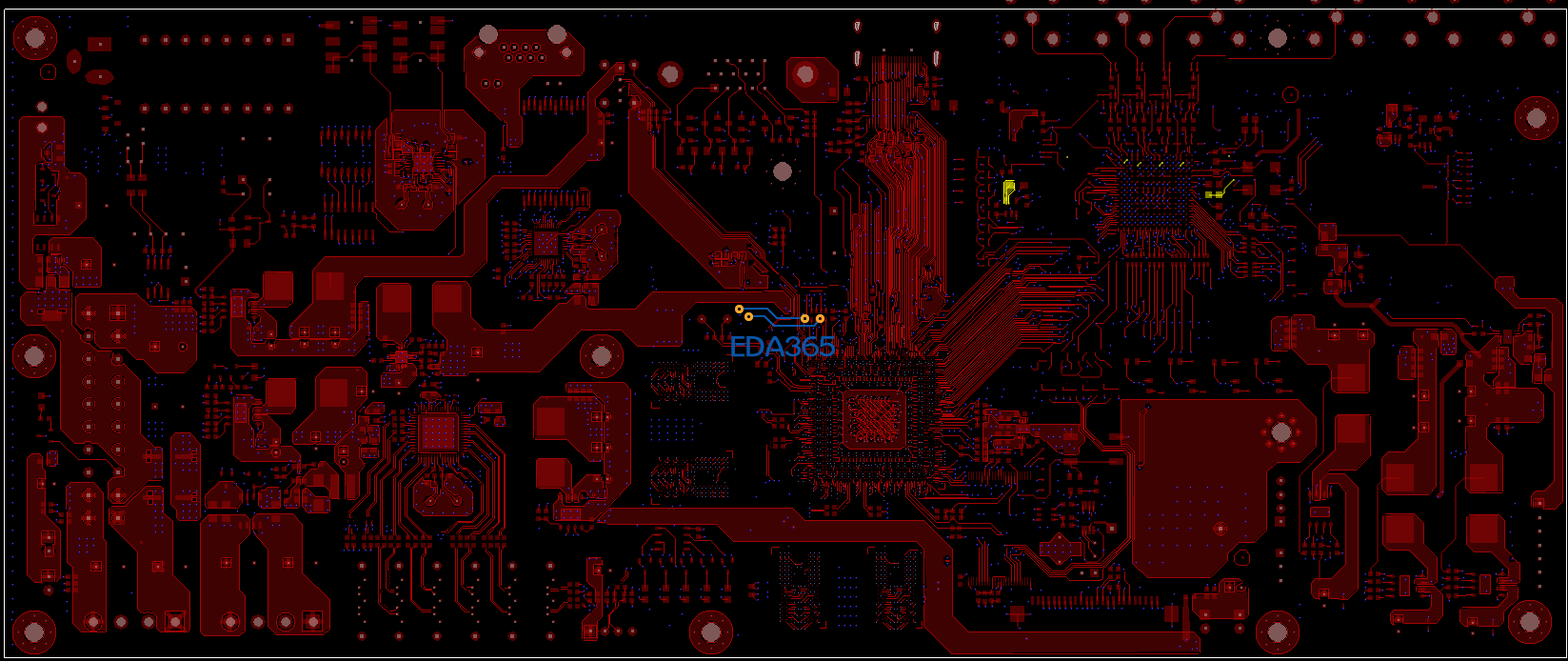

原来板子是做的6层板:

L1: 器件 L2:GND L3:SIGNAL L4:SIGNAL L5:POWER L6 :器件

现在想将层板,DSP芯片可以4层,但是HI3531是推荐用6层的,据说外面有4层板,

如果改的话,我是想最简单,把L2 L5干掉,但是S板子上有DDR走线,担心信号回流有问题,请问问各位大侠有没有问题或者有什么好的建议,谢谢了!

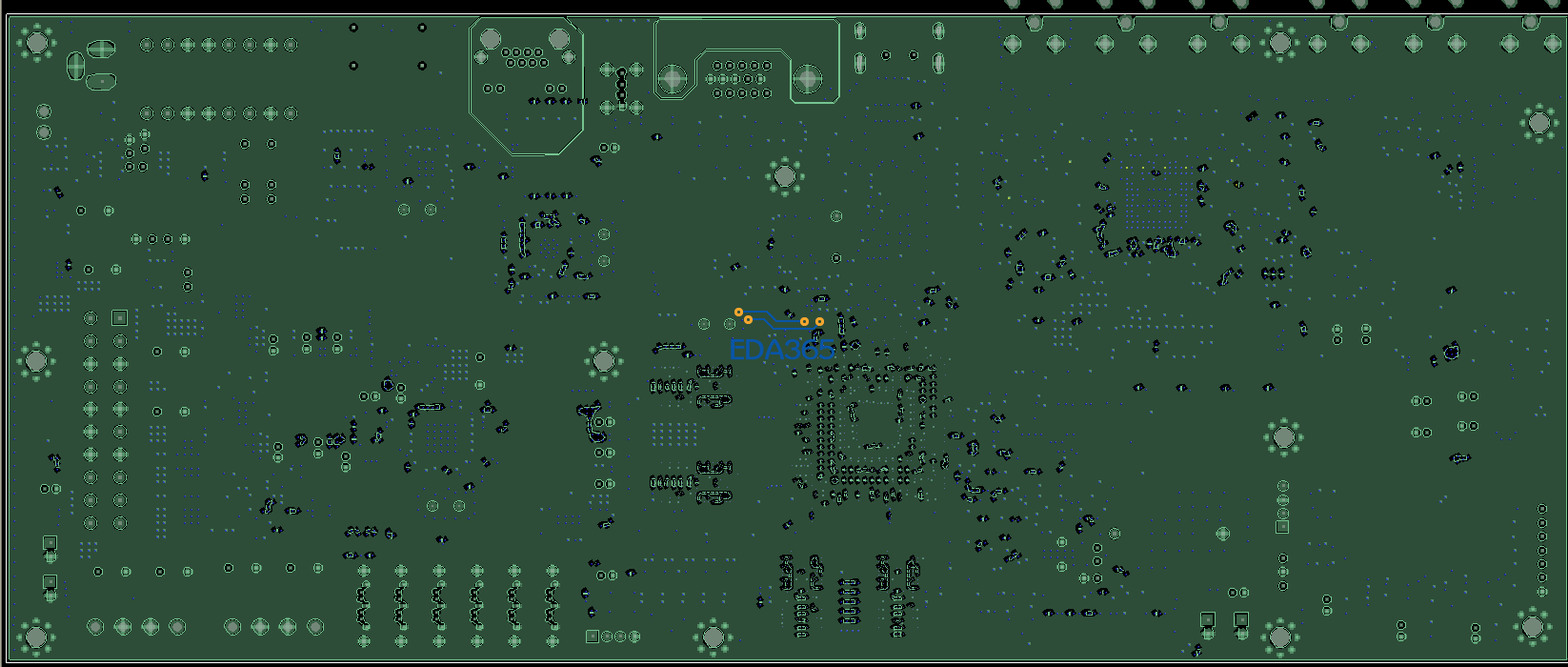

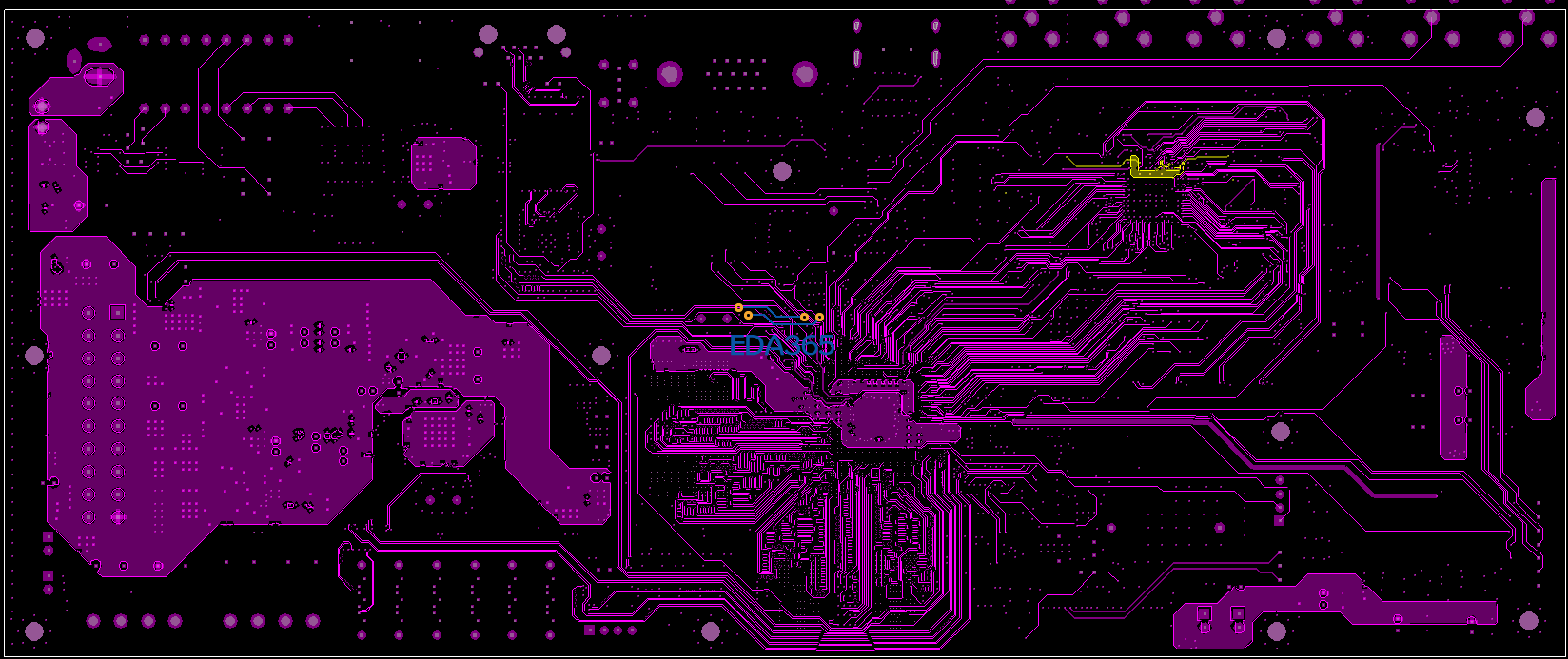

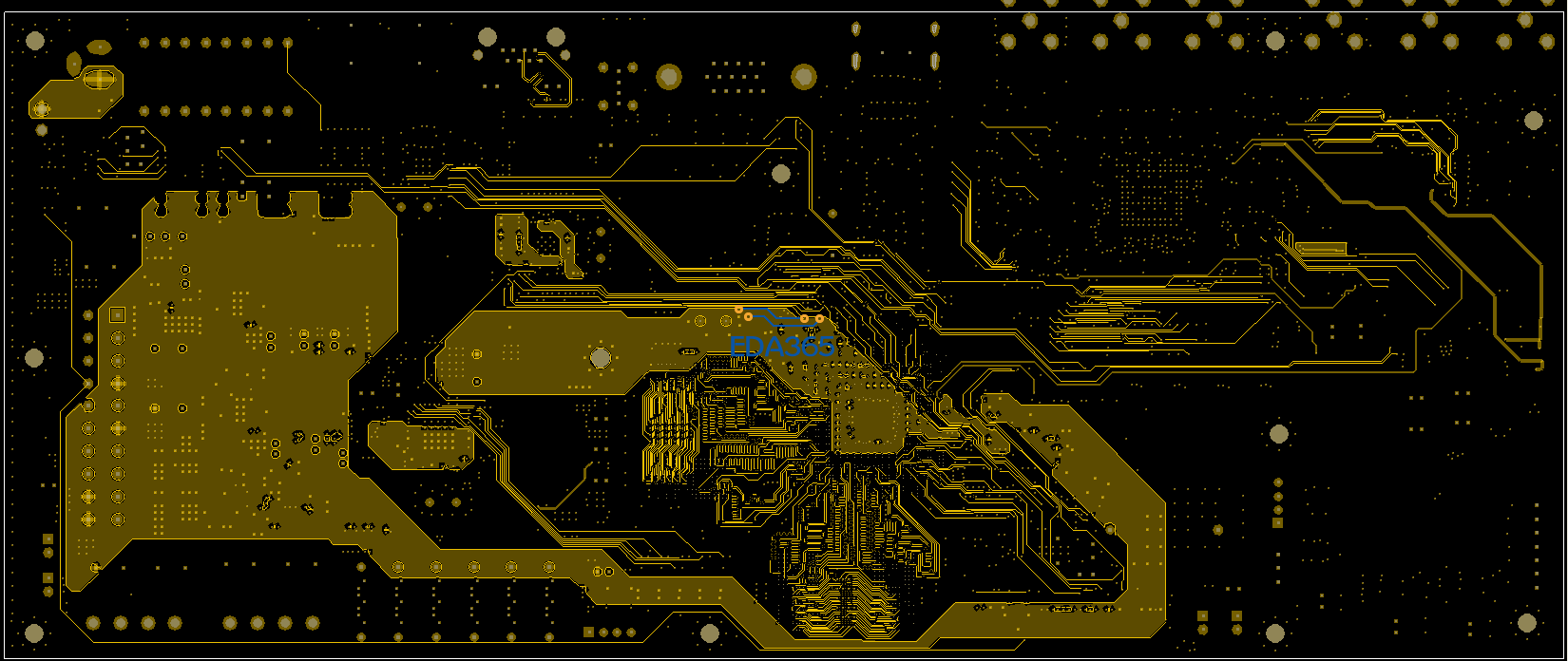

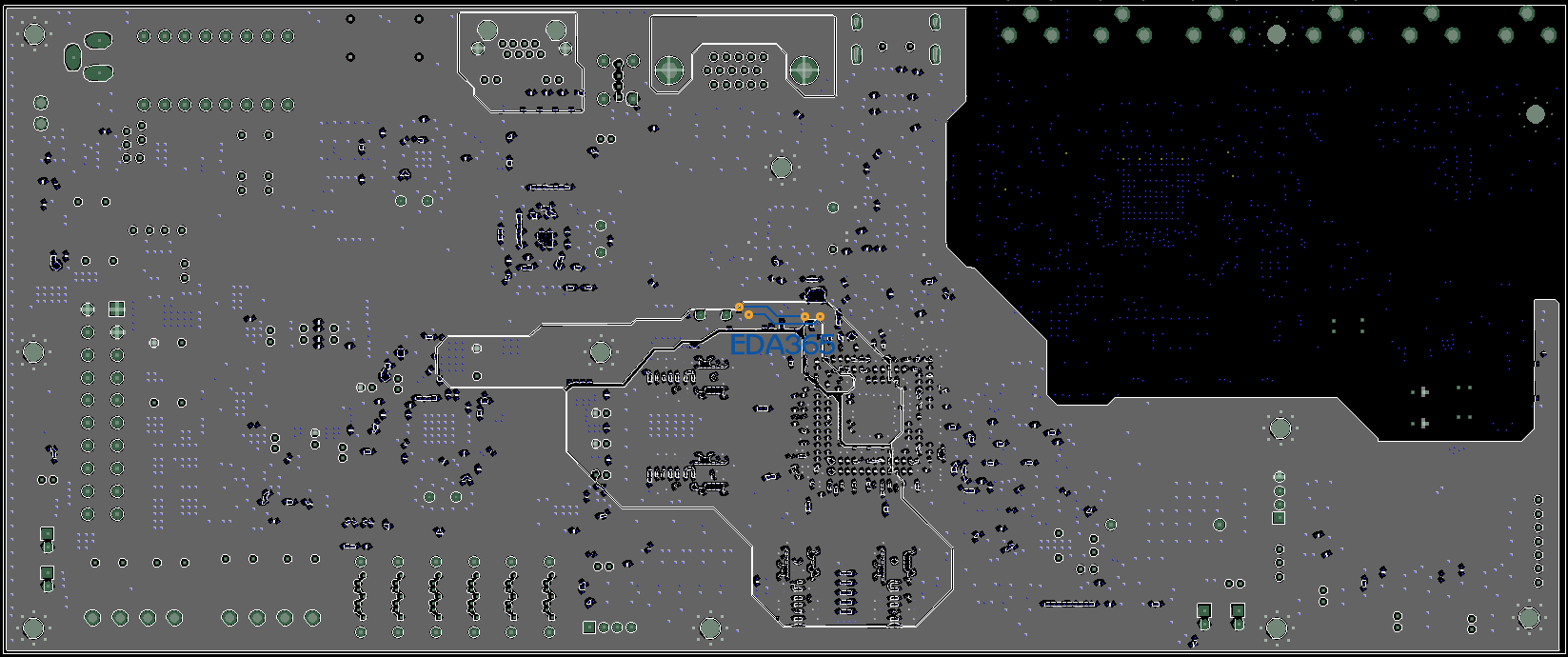

以下是原来每层的线路图:

产品是视频监控的DVR板子,使用的是海思HI3531+公司自己开发的DSP芯片。

原来板子是做的6层板:

L1: 器件 L2:GND L3:SIGNAL L4:SIGNAL L5:POWER L6 :器件

现在想将层板,DSP芯片可以4层,但是HI3531是推荐用6层的,据说外面有4层板,

如果改的话,我是想最简单,把L2 L5干掉,但是S板子上有DDR走线,担心信号回流有问题,请问问各位大侠有没有问题或者有什么好的建议,谢谢了!

以下是原来每层的线路图:

四层板没问题,按sig-gnd-pwr-sig分配就可以了。

HI3531跑的是DDR3-533,应该很好走线。

你原来的6层板的DDR拓扑结构不对,DDR3应该走fly-by,命令控制地址线和时钟线等长,8位一组的数据线和DQM,DQS+-等长就可以了,利用两层可以走完。

LS正解,我还在纳闷了,这是咋回事,看封明明是DDR3,但又走的是T型的。

不过的确是可以,DDR3比DDR2拓扑更好走线,4层可以轻松搞定。