利用锁相环提取调幅信号的载波的一些疑问 ?

这个正弦波输出的还没有听说过

确实,从教学阶段接触的锁相环都TTL或CMOS输出的。

一方面,从集成IC工艺来说,内部集成电容是比较困难和高成本的

另一方面,从VCO输出特点来说,其输出是有频率范围的。那么方波好处是可以保证较好的幅度频率特性,而正弦波幅度更容易收到频率变化影响,不利于鉴相、比较器的稳定工作!

所以我也建议你尽量使用方波来处理,而不要刻意去转成正弦波。

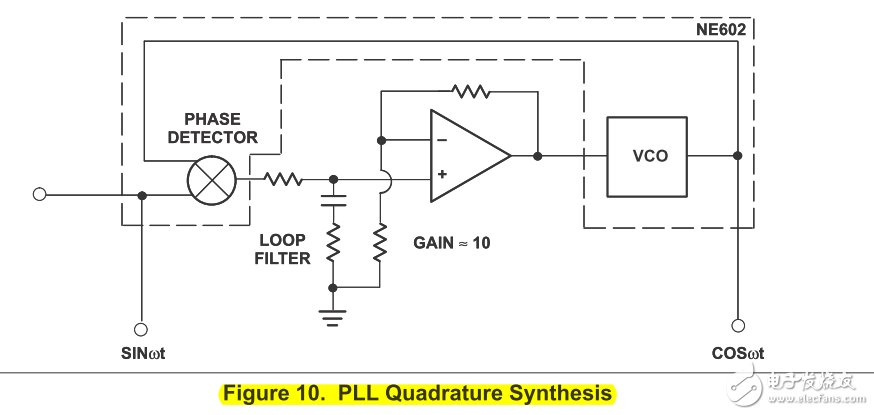

是啊。我就是找不到啊。但是书上的理论说的都好轻松,举得例子,都是正弦进,余弦出。等我一试,回头一看,居然是方波。不知道NE602是不是能够正弦进,余弦出。我有看了这个图:

请问,尽量使用方波来处理是什么意思呢 ? 我是想利用锁相环提取调幅波的载波,都是正余弦信号啊 ? 我目前的想法是,一、找到VCO输出是正余弦的锁相环;二、VCO输出是方波,那我后面接低通滤波器,需要设计一个1MHz的低通滤波器。

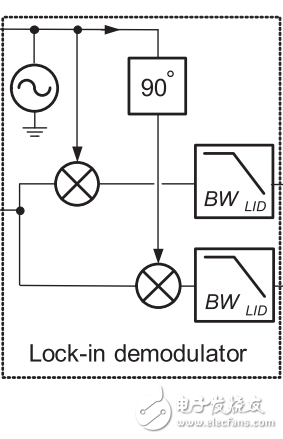

另外,问个题外话,英文文献中的 Lock-in demodulator,是指什么样的解调器 ?

比如这个lock-in demodulator。想问的是lock-in的概念体现在哪里 ?

其实正弦波和余弦波差了180° 我感觉是个180°的滞后放大器

“请问,尽量使用方波来处理是什么意思呢 ?”

----这个是广泛的应用情况出发,一个变频信号通过滤波器后,幅度会发生变化,不利于后级的。而方波只会影响到上升下降沿,有一定的保障幅度的能力,所以对信号处理上有优势。这里先不要太发散。

一、先纠正你一个提法,在信号里面,正弦信号和余弦信号,只是相位差,所以信号类型只有方波、三角波、正弦波信号等等。不要用“正余弦信号”这种提法。

二、回归主题。

按照你的思路提取调幅信号载波。

锁相环作用是锁相输出载波的同频信号,这里要注意,如果调幅信号最小幅度要满足锁相环输入信号要求。

VCO环节输出的是方波或者类似方波。把他变成正弦波,so easy,搞个三阶RC滤波器,完全可以用仿真工具来设计。如果还嫌不够高大上。用MAX293 ,哈哈

图示里面画了两个 滤波器符号,而且标注了是BW带通滤波器。

Lock-in锁相(跟踪频率)就体现在这里。因为锁相环跟踪相位是有范围的(频率范围),超出这个范围,就没有办法锁相了,这就不想当于一个带通滤波器么?

你是说锁相环跟踪频率特性使他充当了一个带通滤波器的作用 ? 感觉这说法虽然没错,但是图上的那两个带通滤波是为了处理解调出来的信号的,这里的lock-in应该不是用在需要解调的信号上的。

调幅信号解调方法有很多,最简单的办法是二极管+电容的包络线提取。但是其缺点就是如果你你有多个信号同时传输,你想提起其中一个特定频率的并解调,那么第一步就是要锁频。所以锁相环充当窄带带通滤波器的设计是最优的选择。

你先画下解调的系统框图。解调调幅载波,你的输出是从VCO出来的。VCO输出有很多高频成分,如果没有很好的带通滤波特性,你可能锁定的是载波的N倍频也说不准。锁相环是闭环的,这里的“滤波器”既是输出同时也是输入!