为后100Gb/s时代挑战做准备

过去,我们可以说某个系统以"X"bps的速度将一些比特从"A"点移至"B"点。但在服务器群有10,000台服务器和千兆存储以后,我们就不能这么说了。今天,设备按照其传输信息时的无误差(BER> 过去,我们可以说某个系统以"X"bps的速度将一些比特从"A"点移至"B"点。但在服务器群有10,000台服务器和千兆存储以后,我们就不能这么说了。今天,设备按照其传输信息时的无误差(BER>10-12)和高效程度来分级。因此引起了一场有关信息传输效率的竞赛--谁的功耗最低,谁就是获胜者。企业运营商关心的是服务器性能和数据传输速度以及系统的能耗。设备运行所需的所有能量以废热的形式存在,因此需要将这种废热排出去,而这个过程又会消耗更多的能量。

以这种方式来看数据传输可能过于简单,但是,不管是用于驱动某条数据通道的集成电路,还是一个每秒数Gb的高性能交换机,任何解决方案的性能计算都应包括功耗。这种衡量指标很像以"纳公顷/两周"为单位表示的硅生产率。从大的方面看,它是对目标本质的简化和概括。在系统周围,使用最少的能源,以最快的速度,实现数据传输。

以下方程式表示了效率分类指标

其中,P为功率(瓦特),REF为无误差通道速率(比特/秒),D为距离(米)。它可以简化为焦耳每比特米(J/b?m),也就是1秒无误差时将1比特数据传输1米所需要的功耗,或者无误差条件下,1比特数据移动1米所消耗的能量。它对各种媒介和编码进行了标准化,并允许使用并排比较技术。

100+ Gbps挑战

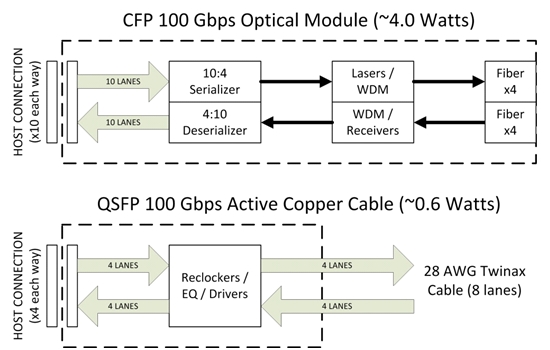

由于我们已经介绍过一种比较各种通信技术的方法,我们将直接讨论数据速率超过100Gbps以后的相关问题。100Gbps数据传输媒介有两种可供选择:光纤和铜线。后一种受限于集肤效应和介电损耗,近远端串扰以及许多其他影响比特误码率的现象。光纤传输过于复杂,并且要求大量功耗,用于将数条电信号转换为通过光纤传输的一个或者多个经过调制的激光束,然后再由激光束转换回电信号(图2)。

图2:100Gbps CFP光纤模块与QSFP有源线缆对比。

半导体行业的主要进展是硅工艺,此外构架方面也获得了一定程度的改进。一些供应商(例如TI)开始使用新的超高性能硅锗工艺实现超低功耗和高成本效益。使用SiGe时,相比CMOS实现方法,驱动器中的发射振幅更高,因而拥有更高的信号完整性。这些工艺结合了新的时钟恢复和前馈均衡技术,可以轻松达到每通道25+ Gbps。下一代设备有望拥有这一数据速率,并计划于2013底上市销售。

对比现有100Gbps通道的传输效率,驱动远距离传输时光纤模块拥有明显优势。但是,当涉及企业内部10米以下的数据传输时,现在所使用的铜缆再次闪耀出它的光芒。1米标准时,光纤无误差传输1比特的能耗大概为80微微焦耳(使用100Gbps CFP,每端的功耗为4W),而铜缆传输1比特的能耗仅为20微微焦耳(使用100 Gbps QSFP,线缆每端的功耗为600mW)。以25Gbps运行的4条原生通道,使用设备对设备(box-to-box)配置时,能耗更低。令人吃惊的是,企业环境的大多数互连距离都小于1米。

超越100Gb/s

通过基板和线缆传输串行化比特的传统方法大多包含非归零(NRZ)二进制编码和误差编码(例如8b/10b)。但是,使用可变长度CAT5/6 UTP线缆的以太网标准(例如1Gbase-T)除外。这种标准的复杂度要求极高,原因是所用导线的带宽有限(<350MHz),并且通道损耗存在不确定性。为了弥补这些不足,标准采用了多层符号编码、位交错、前向纠错、回波消除和大量的其他技术,并与动态链路训练结合,以建立最快的无误差连接。所有这些导致其功耗高于NRZ版本,但在这些情况下,也很难找出一种更好的替代方法。

如果行业把铜线的数据连接速度推高至25Gbps以上,那么问题是,双层(二进制)NRZ编码还会存在吗?即使现在,还有人会说应该放开对25Gbps数据速率的限制。Intel公司建议在企业内部和基层之间也都使用多层编码。由于符号编码比特密度更高,这样可以实现高数据速率,但是能耗也肯定会增高。在今天的市场上,Broadcom和其他公司提供的10Gbase-T解决方案复杂程度也有不断增加的趋势。正如其以前的一些产品,这些器件利用多层信号传输,通过符号编码增加比特密度。利用多条通道(一条CAT7线缆4对),该标准可支持约500MHz有限通道带宽的情况下10Gbps数据传输速率。那么,随着这个行业向40Gbps通道发展,多层方案会代替二进制编码吗?可能会,但是二进制NRZ成熟易懂。市场上有大量的NRZ误码率测试仪及完善的基础设施。另外,还有发射器和接收器复杂性问题。即使CMOS几何尺寸减小至40nm标准以下,功耗和成本都是需要解决的问题。

本文小结

考虑到未来4年市场所需要的器件绝对数量,思科VNI的预测数据相当令人激动。同时,它也为有线和无线基础设施供应商以及提供媒体和信息的数据服务器带来了一些问题。所有这些

- 以太网接入技术简介(01-09)

- 以太网技术的发展(01-24)

- 基于PC104总线的嵌入式以太网卡设计(01-31)

- 下一代SDH技术发展趋势及应用分析(中)(01-05)

- PLC(电力线通信)技术简介(01-08)

- 电信接入网设备的安全和过压防护测试(01-08)