以太网端口保护需要智能化策略

体设计。

很多情况下,PHY GND与PCB的模拟地都是隔离的。这是使用耦合变压器的一个优势。在这种情况下,变压器上应只耦合很少的能量。不过由于绕组间电容的影响,TVS1与变压器相结合不会阻止所有的能量传送至PHY端。这些能量将通过变压器的磁性元件经由电容耦合到其驱动器侧,这些能量可能会在以太网PHY出现共模或差分事件(或者两者同时出现)时产生。

为符合IEEE 802.3标准的隔离要求,图2中的线路侧保护器件TVS1可能不会将其接地引脚(2、3、6和7)接地。尽管根据IEEE 802.3对UL-60950-1的引用,这种接地连接可被允许。如图2所示,TVS2始终将其I/O引脚连接至差分对。

图2:在两个引脚之间的RJ-45端口处出现浪涌事件时,大部分能量在线路端保护装置中耗散,而部分能量则通过变压器在变压器驱动器侧产生共模或差分事件。

不过,与线路侧保护器件不同的是,该器件将其接地引脚连接至局部地平面,并将其参考引脚连接至PHY VCC(Littelfuse公司建议使用这种配置)。如果未连接接地引脚的话,TVS2就会仅成为差分保护器件,并会潜在地允许具有破坏性的共模事件通过未箝制的PHY。

静电放电

静电放电(ESD)是小电路走线和器件的常见威胁。静电放电是由人体的静电电荷传输到电路所引起的,瞬态电压峰值高达15kV并不常见。在不太严重的情况下,ESD可能会导致错误的电路操作或者之后将发展成彻底故障的潜在缺陷。

ESD抑制器必须具有极快的响应时间,频繁地处理持续时间较短的高峰值电压和电流。TVS二极管阵列是箝位器件,可将瞬态电压限制在设定值。TVS的低动态电阻使其能够在超出其箝位阈值时,将这些高压ESD事件箝制在极低的电平(想想I×R)。一旦瞬态电压降到TVS器件的反向断态电压以下,TVS器件就将停止传导。

根据IEC61000-4-2标准,进行抗ESD测试的设备将通过接触和空气放电来进行测试。在测试中注入ESD的方法非常之多,比如IEC61000-4-2标准中给出的一些方法。但是在任何情况下,ESD脉冲都是以RJ-45连接器线路侧的共模事件出现,因为此放电事件以地为参考。保护器件被连接在一起,并根据上文讨论的共模事件进行测试。

电快速瞬变

根据IEC61000-4-4,进行抗EFT测试的设备与进行共模雷击浪涌的测试非常相似。在图3所示的较典型的配置中,所有的导体(或引脚)都连接至测试发生器的正极端,并相对GND产生浪涌。

图3:在电快速瞬变(EFT)测试的典型配置中,所有的导体/引脚都连接至测试发生器的正极端。施加的浪涌是以地为参考施加的。

若不是在以太网供电(PoE)应用中,就不需要使用耦合电容器,在以太网供电应用中,33nF的电容值应该就已足够。如果数据线路具有良好均衡,那么双绞线对之间就只有很少的差分能量或者不存在差分能量。不过,变压器的耦合电容还是会将共模能量传送到驱动器端,尽管能量有所减少。

电缆放电事件

电缆放电事件(CDE)在产生方式和波形特性方面都不同于ESD。CDE事件一般是在PVC包覆的CAT5非屏蔽双绞线(UTP)电缆拉在尼龙地毯或者瓷砖地板上时发生的,因为这种地板会导致电荷在电缆上逐渐聚集。同样,通过导管或者其他网络电缆铺设时,电荷也会在电缆上聚集。双绞线电缆由于储存了电荷,因此就像电容一样。

不过,只有当电缆无终端,并且电荷不会立即耗散时(即电缆的两端未插入系统),电荷才会逐渐聚集在一起。新型CAT5和CAT6电缆的介电泄漏极低,往往可以将电荷保持很长一段时间。在相对湿度较低的环境中,电荷保持时间会延长。

当带电的UTP电缆插入RJ-45网络端口时,将有很多可能的放电通路。这种瞬态电流会选择电感最低的通路,可能是位于穿过Bob Smith交流终端或者硅器件的变压器中的两条PCB走线之间的RJ-45连接器。这样,以太网收发器或者上述提到的任何器件都会受损。

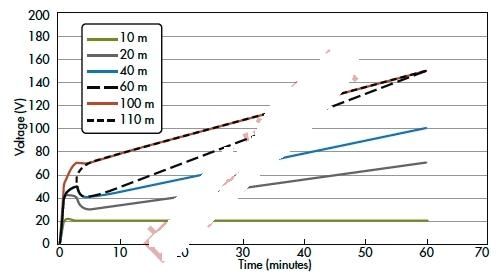

电荷量取决于电缆的长度(图4)。研究表明,无终端的双绞线电缆可以累积高达几千伏的电荷。对于电缆长度超过60m的系统,应采取额外的CDE预防措施。

图4:不同长度的CAT5以太网电缆的电压主要是由于静电电荷随时间的积累而形成。本图显示了长度从10m至110m的电缆的特性曲线。

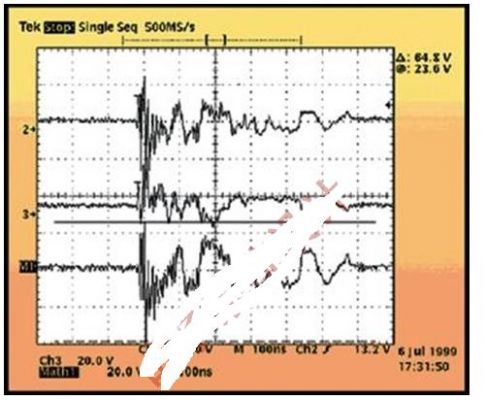

CDE波形并不像上文所述的任何一种其他的威胁。根据耦合机制的不同,CDE可以是差分的,也可以是共模的。虽然它可能有很大变化,不过其一般特性是具有表现电压和电流驱动的高能量。波形在数百纳秒的时间内展开,同时实现快速极性翻转(图5)。在这个实验中,PHY的发送器受到损坏,无法发射网络上的封包。

图5:图示显示了在25ft双绞线被充电至1.5kV后,以太网PHY的发送器引脚处的破坏性CDE波形。

系统设计人员可

- 以太网接入技术简介(01-09)

- 以太网技术的发展(01-24)

- 基于PC104总线的嵌入式以太网卡设计(01-31)

- 下一代SDH技术发展趋势及应用分析(中)(01-05)

- PLC(电力线通信)技术简介(01-08)

- 电信接入网设备的安全和过压防护测试(01-08)