OFDM硬件结构

时间:04-10

来源:eNet硅谷动力

点击:

OFDM|0">OFDM调制解调与常规调制解调相比,所需的运算量大,尤其是当系统选用的子载波个数多时,仅在发射端的IFFT变换和接收端的FFT变换所需的时间就很长。通常使用FPGA和高速的DSP解决该问题。由于在接收端还要完成信号突发检测、同步和频偏校正等数字信号处理,所以接收端对实时性要求更高。在该系统中,使用FPGA完成信号的突发检测和定时,DSP完成FFT/IFFT变换和QAM/QPSK调制解调。

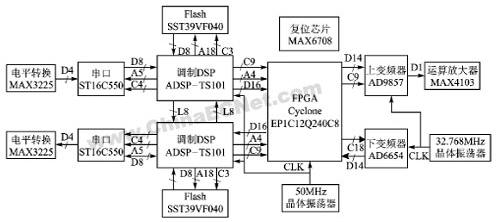

本系统主要由4部分组成:DSP、FPGA、正交数字上变频器(QuadratureDigitalUpconverter)、正交数字下变频器(Quadrature Digital Downconverter)。系统硬件结构如图2所示。图中,D表示数据总线,A表示地址总线,C表示控制总线, L表示链路口数据线, 字母后面的数字表示总线的位数。50 MHz晶振为两片DSP及FPGA提供时钟信号,32.768 MHz高稳定度晶振为AD9857和AD6654提供高质量的时钟信号。复位芯片MAX6708控制DSP、FPGA、AD9857、AD6654和ST16C550的复位。

系统硬件结构

DSP完成QAM或QPSK的调制解调和FFT/IFFT变换。系统所使用的DSP[2]是ADI公司的TigersharcTS101。该DSP具有以下特性:最高工作频率为300 MHz,3.3 ns指令周期;6 MB片内SRAM;2个计算模块,每个模块都有1个ALU、1个乘法器、1个移位寄存器和1个寄存器组;2个整型ALU,用来提供寻址和指针操作;14个DMA控制器;1149.1 IEEE JTAG口。对于OFDM基带处理,该DSP最大的特点是: 进行256点的复数FFT变换,仅需3.67 μs。

正交数字上变频器采用ADI公司的AD9857。AD9857[34]最高工作频率为200MHz,输出中频频率范围为0~80MHz;内部集成半带滤波器、CIC(CascadedIntegrator Comb)滤波器, 反SINC滤波器和高速的14位数/模转换器,其核心是一个相位连续的直接数字频率合成器DDS (Direct Digital Synthesizer)。在该方案中,AD9857工作在正交调制模式,其32位频率控制字使输出频率的最高精确度为:SYSCLK(系统时钟)除以232。

正交数字下变频器采用ADI公司的AD6654。AD6654[5]内部集成了一个14位、92.16Msps的模/数转换器和4/6通道的数字下变频器。每个通道可独立配置。数字下变频内部集成了频率变换器、可编程级联梳状滤波器(CIC)、2个滤波器组和数字自动增益控制。其中:频率变换是通过32位数控振荡器实现的;CIC实现1~32倍的抽取;2个滤波器组包括FIR滤波器和2倍抽取的半带滤波器。输入的中频模拟信号经过ADC和频率变换后,使用滤波器组进行滤波和抽取,最后并行输出正交基带数字信号。输入中频信号频率最高可到200MHz,此时,使用欠采样技术。

本系统主要由4部分组成:DSP、FPGA、正交数字上变频器(QuadratureDigitalUpconverter)、正交数字下变频器(Quadrature Digital Downconverter)。系统硬件结构如图2所示。图中,D表示数据总线,A表示地址总线,C表示控制总线, L表示链路口数据线, 字母后面的数字表示总线的位数。50 MHz晶振为两片DSP及FPGA提供时钟信号,32.768 MHz高稳定度晶振为AD9857和AD6654提供高质量的时钟信号。复位芯片MAX6708控制DSP、FPGA、AD9857、AD6654和ST16C550的复位。

系统硬件结构

DSP完成QAM或QPSK的调制解调和FFT/IFFT变换。系统所使用的DSP[2]是ADI公司的TigersharcTS101。该DSP具有以下特性:最高工作频率为300 MHz,3.3 ns指令周期;6 MB片内SRAM;2个计算模块,每个模块都有1个ALU、1个乘法器、1个移位寄存器和1个寄存器组;2个整型ALU,用来提供寻址和指针操作;14个DMA控制器;1149.1 IEEE JTAG口。对于OFDM基带处理,该DSP最大的特点是: 进行256点的复数FFT变换,仅需3.67 μs。

正交数字上变频器采用ADI公司的AD9857。AD9857[34]最高工作频率为200MHz,输出中频频率范围为0~80MHz;内部集成半带滤波器、CIC(CascadedIntegrator Comb)滤波器, 反SINC滤波器和高速的14位数/模转换器,其核心是一个相位连续的直接数字频率合成器DDS (Direct Digital Synthesizer)。在该方案中,AD9857工作在正交调制模式,其32位频率控制字使输出频率的最高精确度为:SYSCLK(系统时钟)除以232。

正交数字下变频器采用ADI公司的AD6654。AD6654[5]内部集成了一个14位、92.16Msps的模/数转换器和4/6通道的数字下变频器。每个通道可独立配置。数字下变频内部集成了频率变换器、可编程级联梳状滤波器(CIC)、2个滤波器组和数字自动增益控制。其中:频率变换是通过32位数控振荡器实现的;CIC实现1~32倍的抽取;2个滤波器组包括FIR滤波器和2倍抽取的半带滤波器。输入的中频模拟信号经过ADC和频率变换后,使用滤波器组进行滤波和抽取,最后并行输出正交基带数字信号。输入中频信号频率最高可到200MHz,此时,使用欠采样技术。

- 宋俊德:3G与WIMAX竞争中融合 终端内容趋同(08-23)

- 全球WiMAX论坛主席Ronald Resnick演讲(08-23)

- 多载波技术在3G网络部署中的应用(09-11)

- MIMO OFDM无线局域网研究及关键技术(10-16)

- Comsys:集成移动WiMAX将是手机下一轮技术趋势之一(11-18)

- 802.16b系统物理层基于OFDM接入优越性 (01-01)