实用可控的按键抖动消除电路

1 问题的提出

研制测量仪表及电子仪器的过程中,常常遇到按键抖动的问题,即虽然只是按下按键一次然后放掉,结果在按键信号稳定前后,竟出现了一些不该存在的噪声,这样就会引起电路的误动作。在很多应用按键的场合,要求具有消抖措施,即对于噪声信号消抖电路输出信号为零(消抖电路屏蔽了噪声信号,表示按键没有动作),只有当按键信号K稳定下来甚至经过一定的时间消抖电路才产生输出信号Y。按键信号K消除,消抖电路输出信号Y随之消失。

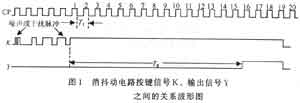

笔者根据某用户的具体要求设计了具有高抗噪声特性的、延时时间精密可控的消抖动电路,其按键信号K、输出信号Y之间的关系如图1所示。

|

|

2 电路组成及工作原理

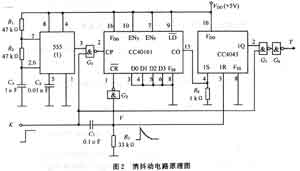

延时时间精密可控的消抖动电路的原理图如图2所示。该电路由4块CMOS集成芯片和若干电阻、电容组成。

其中555定时器组成多谐振荡器用来给计数器提供时钟脉冲;1块CC40161型四位同步二进制计数器用来设定消抖动电路输出信号Y的延迟脉冲个数。1块CC4043四R/S锁存器(只用了1组,其余3组未用)和1块CC4011四2输入与非门用来实现信号的锁存和控制。

当按键信号K由低电平变为高电平时,电阻尺3和电容C3组成的微分电路使V点产生一个正脉冲,该正脉冲一路经与非门G2反相后加到计数器CC40161的CR端使其清零;另一路加到锁存器CC4043的1R端(此时由于计数器没有进位输出,CO端为低电平,即lS端为低电平),使锁存器输出端1Q为低电子。与此同时,按键信号K已加到了与非门G1的输入端使G1门开门,那么,由555定时器组成的时钟信号发生器3端输出的时钟脉冲通过与非门G1加到计数器的CP端,计数器开始计数。计到15个脉冲,计数器产生进位信号,其CO端输出高电平,使锁存器的1Q端变为高电平,该信号加到与非门G3的一个输入端(与非门G3的另一个输入端为K,已为高电平),则与非门G4的输出Y端为高电平;只有当按键信号K由高电平为低电平时,Y端才随之变为低电平。 另一方面,由于按键信号K变为低电平,封锁了G1门,时钟脉冲不能通过G1门到达计数器的CP端,计数停止。

当出现干扰脉冲时,计数器也计数,但只要干扰冲的宽度小于15个CP脉冲宽度,计数器的进位输陆号CO端就保持低电平,那么Y信号为低电平,即际脉冲的影响不会出现在Y端。

可以用置数法或复位法将十六进制计数器CC40161接成任意进制计数器,然后通过任意进位信号控制1S端的电位,来调整消抖动电路输出信号Y的延迟时间。

|

|

3 数据计算

555定时器组成的时钟信号发生器产生的CP脉冲的周期为:

T1=ln(R1+2R2)C1

CP脉冲的占空比为:

q=( R1+ R2)/(R1+2 R2)

按图中所给参数计算,CP脉冲的周期T1=0.1s,CP脉冲的占空比为:

q=2/3。

消抖动电路输出信号Y的延迟时间为:

Td=15Tl=151n2(Rl+2R2)C1

按图中参数计算Td=1.5s

4 电路特点

(1)该电路由CMOS集成芯片组成,功耗低,抗干扰能力强。

(2)从按键信号K到消抖电路产生稳定的输出信号Y的延迟时间Td稳定、可调。

(3)每当按键信号K到来(由低电平变为高电平),均自动使计数器清零,不需另外加入复位脉冲。

(4)按键信号K消除,计数器自动停止计数,不需另外设置开关。 该电路除用于消除按键的抖动外,还可用于需要产生一定延时控制的任何电路中。该电路为利用单片机和CPLD(Complex Programmable Logic Device)实现软件消抖提供了设计思想。