正确理解时钟器件的抖动性能

锁相环时钟器件

随着半导体制造工艺的迅速发展,模拟半导体行业演进到130nm或65nm节点时,意味模拟器件的集成度可以越来越高。目前,单芯片集成锁相环时钟IC芯片,可以实现多锁相环集成、多VCO集成以及时钟分布电路于一体,时钟器件种类繁多,同时有些器件即可作为时钟合成器应用,也可用作抖动滤除功能实现高性能时钟输出。

时钟合成器(CSU)

也称为时钟倍频器(CMU),对输入信号进行倍频以产生各种不同频率的输出,若参考时钟为本地振荡器或内部集成时,也称为时钟发生器(Clock Generator)。根据应用场景的不同,目前集成IC内部压控振荡器通常采用采用环形振荡器和LC振荡器。环形振荡器的调谐范围更宽、功耗更低,而且芯片面交更小等,被大量应用在对集成度要求较高的应用场景,而LC振荡器具有品质因数Q值高的优势,噪声性能较环形振荡器好,被广泛引用于对抖动指标有较高要求的通信、医疗等领域。

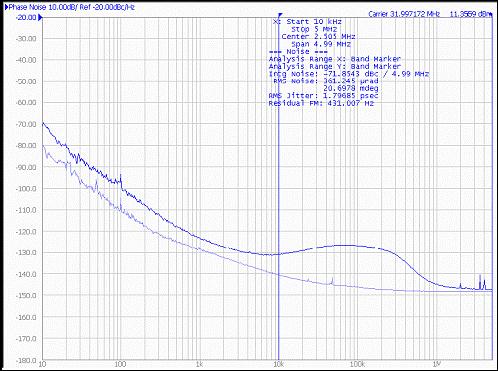

当时钟器件作为时钟合成器应用时,环路带宽通常是在100KHz~400KHz左右,根据具体应用场景,如输入频率和输出频率不同,环路带宽和相位余量可有差异。因此,时钟合成器输出抖动主要由参考时钟噪声分布和本地振荡器的噪声分布共同决定。作为一颗在消费类终端产品应用的时钟合成器件,CDCE706的输出相位噪声如图8所示,均值抖动为1.8ps@10KHz~5MHz,可满足大多数消费类产品的应用需求。

图10 CDCE706时钟合成器的输出抖动性能

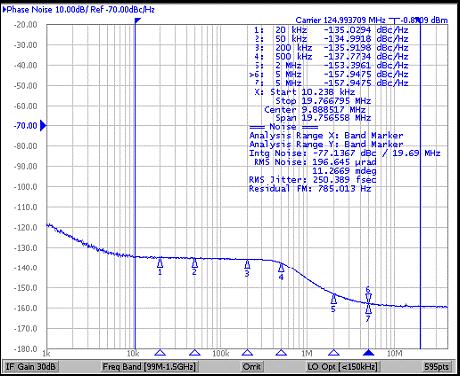

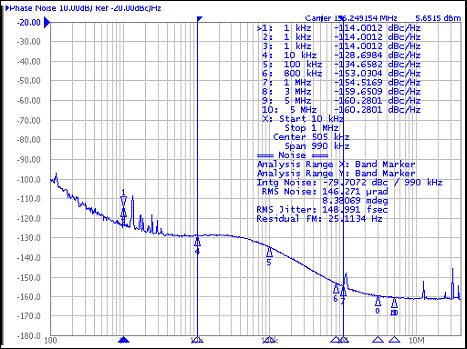

在数据通信系统中,往往需要高抖动性能的时钟发生器,如均值抖动指标Jrms<1ps@(12KHz~20MHz),此时可采用高性能时钟合成器。由于集成IC芯片内部的压控振荡器长期稳定性较差,相应的近端噪声比基于晶体的振荡器抖动性能要差,因此时钟合成器的参考输入信号可选择来自晶振或压控晶体振荡器等具有较干净近端噪声的信号源,经内部高频锁相环电路实现频率倍频和频率转换功能,如德州仪器推出的高性能集成IC锁相环芯片CDCM6208、LMK03806等,图11是CDCM6208作为时钟合成器时一个典型的输出相位噪声(输入来自25MHz晶体XTAL),图12是LMK03806典型的输出相位噪声,两者都是目前抖动性能指标最优秀的频率合成器之一。

图11 CDCM6208输出相位噪声(时钟合成器模式)

图12 LMK03806输出相位噪声

- 鉴频鉴相器的指标对锁相环死区及抖动性能的影(12-08)