标准线性集成电路的电诱发损坏:最常见起因和防止再发生的相关处理

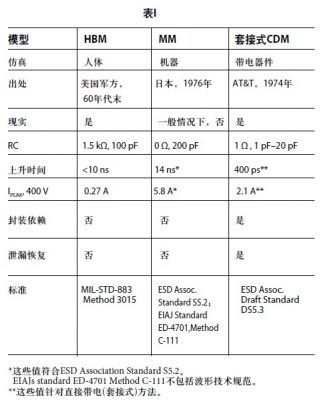

ESD模型小结

表I是比较三种ESD仿真模型的最重要特性的参考。

预防

审查将采取ESD保护措施的设备时,应考虑以下因素:

• 必须有一个接地工作台来处理静电敏感器件,结合使用以下装置:

a)个人接地带(防静电手环)

b)导电托盘或分流器等

c)导电工作台

d)导电地板或地垫

e)一个公共接地点

• 所有用于存储器件的钢架或机柜必须接地。

• 应控制相对湿度;理想范围是40%至60%。在无法维持高相对湿度水平的地方,应使用电离空气来驱散静电

电荷。

• 区域中使用的所有电气设备必须接地。

• 禁止使用易产生静电的器材,例如透明胶带。

• 后续至少每隔三个月做一次ESD审查。

• 培训:切记有效ESD控制程序的关键是"培训"。所有接触集成电路的人员都应进行培训并且培训要记录归档作认证之用,例如ISO9000审计。

确定器件是否是由于ESD或电气过应力(EOS)而发生故障较为困难,一般最好交由故障分析工程师处理。执行电气分析和内部可视分析时,ESD损害一般没有EOS的损害明显。对于ESD,1 kV或以上(取决于器件的ESD额定值)的事件会毁坏氧化层(管芯的层间电介质)并在10ns以内损坏结点(见图6)。或者,EOS条件导致持续时间大于1 ms的1至3 A电流,使焊线产生足够多自热效应而被熔断。闩锁会造成此类条件发生。较低的电流会导致芯片金属化层及其他互连层的快速熔化(见图5)。

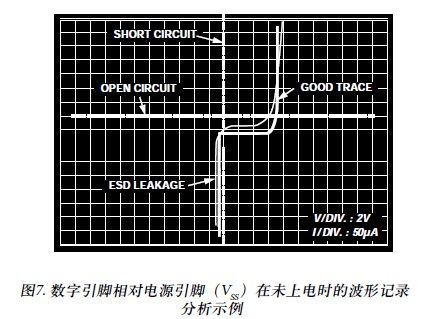

可以在相应位置上执行快速分析来评估器件是否受到过应力或可能遭受ESD事件。为了执行此分析,比较嫌疑器件和已知正常器件的引脚到引脚I/V结果,应使用波形记录器或类似设备。12位DAC的数字输入引脚(以VSS电源引脚为参考)上的一组典型短路、开路或ESD泄漏I/V迹线如图7所示。

闩锁

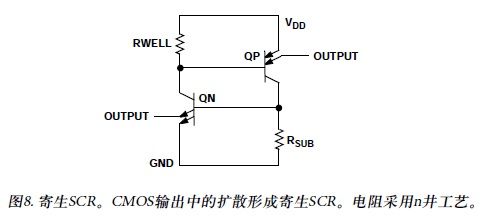

闩锁是一种潜在破坏性情况。这种情况会触发一个寄生有源元件,造成正负电源短路。如果电流不受限制,会发生电气过应力。闩锁的典型情况发生在CMOS输出器件中,两个寄生基-射结之一在过压事件期间暂时正向偏置时,驱动器晶体管和井形成pnpn SCR结构。SCR的开启本质上造成VDD和地之间的短路。

触发机制

有两种主要触发机制。首先,如果输入/输出(I/O)引脚电压升至正电源电压以上,或降至负电源电压以下,寄生晶体管之一会开启。通过集电极返回电源的电流引起第二寄生晶体管的基极-发射极上的压降。然后,第二晶体管的集电极电流使第一晶体管的基极-发射极上保持正向偏置。如果两个晶体管增益之积大于单位增益,该条件可能自持续,并且甚至在消除外部电压之后仍持续存在。

如果在I/O引脚处存在过度电压过冲,或者如果在给器件供电之前有信号到达输入端,或者由于静电放电原因,便会发生此触发机制。此闩锁一般限于直接连接到引脚的元件。

图9b电流倍增。衬底电压上升主动将第二个寄生晶体管偏置为导通。然后,电子电流在n井里引起压降,进一步开启第一个晶体管。如果电流增益之积大于1,电源之间的最终电流可以自持续,仅受内部电阻(即,SCR)限制。

虽然触发是由过压事件(一般只是在电源电压之上或之下一个二极管压降)引起,行业惯例是根据在内部寄生电阻上产生出足以维持闩锁条件的压降之前引脚在过压条件下能耐受的过电流量(源电流或吸电流)对I/O进行分类。一般认为能耐受100 mA已足够,若能耐受200 mA则认为该器件不受闩锁影响。

第二种触发机制是在电源电压升至足以击穿一个内部结的条件下发生,可将电流注入前述SCR中。此触发机制可由电源瞬态或由旁路到一条供电轨的静电放电引起。与I/O触发情况不同,闩锁可发生在管芯的任何地方,并不限于外部电源连接或I/O引脚附近。

对电源过压的耐受性通常受制造器件的加工工艺限制,可查阅数据手册的"绝对最大额定值"规格。如果超过此额定值,可能发生永久EOS损害。使器件工作在接近最大额定值可能会降低器件的长期可靠性。同样,电气规格仅适用于数据手册上规定的电源,超出这些额定值范围将不予保证。

设计规则

以下是所有使用CMOS和Bipolar-CMOS IC的设计人员需要遵守的一组规则:

1. 在任何时候都不允许数字输入和输出超过VDD 0.3 V以上。这包括VDD = 0 V时的关断情况。

2. 亦不允许数字输入和输出降至低于DGND –0.3 V以上。

3. 对于混合信号器件,不允许DGND超过AGND 0.3 V。

4. 对于CMOS或Bipolar-CMOS DAC,一般不允许IOUT降至低于AGND 0.3 V以上。部分DAC可容许较大IOUT电流,无任何闩锁危险。

- 深入分析运算放大器过压保护技术(07-19)

- PulseGuard ESD抑制器在便携式设备中的应用(05-06)

- MAX2140内部ESD二极管的保护电路设计(07-14)

- CMOS集成电路中ESD保护技术研究(10-17)

- 可靠性工程——关于电子设备静电放电(ESD)防护的设计原则(10-30)

- 关断检流放大器的两种基本方法(02-14)