高速数据线的应用及其电路保护

IC行业正发生重大变化,特别是用于全新高速数据线的系统级芯片(SoC),例如SuperSpeed USB、MHL、HDMI、DisplayPort和eSATA,需要使用最先进的CMOS工艺。由于ESD保护电路无法根据摩尔定律按比例缩小,这些集成了ESD保护电路的SoC通常仅设计成在装配工艺具有良好保护措施时无损。然而,更为严重的是,完整的系统——如手机、平板电脑或普通电脑等——在常温环境条件下使用时极易遭受ESD冲击。另外,接口SoC特别容易受到静电放电的影响。本文讨论高速数据线的某些应用需求,以及根据这些需求,保护设备应采用的型号和技术。

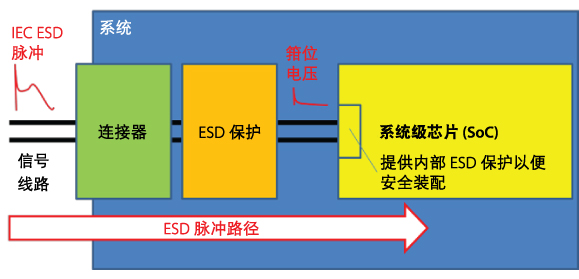

要获得系统级的稳固度以抵抗场级ESD冲击,根据IEC 61000-4-2标准,需采用专门的ESD保护器件,且最好放置在连接器后面(图1)。

图1:器件级和系统级ESD保护。ESD保护可降低ESD脉冲所产生的剩余箝位电压。数据速率越快,SoC对该箝位电压也就越敏感。要按照IEC61000-4-2标准来保护整个系统使其免受ESD冲击,则ESD保护必须使ESD脉冲低于SoC的安全值。

对于想要理解SoC受何种保护程度的人来说,ESD保护设备数据手册中的IEC61000-4-2标准无法给出解答。它只给出了最大ESD脉冲,在该脉冲下,ESD保护器件自身无损。然而,根据IEC61000-4-2,当涉及带ESD保护器件的系统和现代SoC的ESD脉冲保护时,目前较为普遍的是,ESD冲击发生时外部保护设备无损但SoC因过压而损坏。问题是,如何才能有效保护这种情况下的SoC?

了解ESD保护和SoC之间相互作用的特点

首先,让我们看看SoC的要求。高度集成的工艺具有较低的工作电压,因此电路板上针对SoC的ESD保护在电压极低时便开始作出反应,以保护栅极氧化层不被过压击穿。工艺先进SoC的工作频率高意味着它们将对ESD冲击作出快速反应。结果便是,良好的外部ESD保护设备也需要对ESD脉冲作出极快的反应,这就需要具有较低的触发和箝位电压,并必须设计为可负载大部分ESD电流,以降低SoC的ESD电流负载。

在尽可能简单的模型里,SoC和ESD保护器件通过并联方式连接。当静态电流流过时,该电流为SoC和ESD器件所共有,并与它们的输入电阻成反比。然而,由于两者都会作出反应,SoC和ESD保护器件针对ESD脉冲的保护是非线性的,因此光有这个静态模型是不够的;波形记录仪无法表示出单个设备——或整个系统——针对ESD脉冲的反应。除此之外,静态测量也会导致被测设备(DUT)过早地被判定为不合格。

要确定被测设备在ESD事件下的动态特性,可使用传输线路脉冲(或简称为TLP)测量作为标准表征工具。阻抗通常为50 Ω的已定义传输线路由TLP测量充电并且通过被测设备完成放电。要避免信号失真,首选恒定阻抗系统。它可以产生定义明确的矩形脉冲,输出定义明确的电流和电压值。重复该测量时如果采用更高电能,便可得到下一组电流-电压值,直到完成I-V图形,或者直到被测设备损坏。要在测量早期捕获到被测设备的损坏情况——开始时可能略为有所退化——可在每个TLP脉冲之后检测漏电流。

- 电路鲁棒性的设计影响因素(09-10)

- 亚微米CMOS电路中VDD-VSSESD保护结构设计(03-23)

- 安森美电路保护及滤波技术解析(06-16)

- MAX14780E ESD保护的RS-485/RS-422收(02-17)

- 电源线路滤波器中的漏电流(02-03)

- 关断检流放大器的两种基本方法(02-14)