检测放大器偏移问题

您是否曾经有过在为您的电路选择最佳运算放大器上花费了大量时间但最后却发现厂商基准输入的失调电压不对的经历?在跨阻抗放大器、模拟滤波器、采样保持电路、积分器、电容传感器或者任何其他您放大器周围有高阻抗组件的电路中,如果您将放大器作为关键组件来使用,那么您可能会发现放大器的输入偏置电流在您电路的电阻中形成了一个失调电压误差。

在双极放大器年代,术语"输入偏置电流"是一个准确的描述,而现在也是如此。双极放大器的输入偏置电流在放大器的输入端与 NPN 或 PNP 晶体管的基电流相同。双极放大器输入偏置电流的幅

度范围从低功耗器件的数毫微安到高功耗器件的数百毫微安。

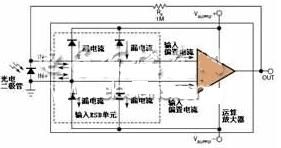

当您研究 JFET 或者 CMOS 输入放大器时,术语"输入偏置电流"便失去了它的意义。使用这类放大器,从放大器输入引脚下拉或者吸取的电流实际上为输入 ESD(静电放电)单元(请参见图 1)的漏电流。

图1 输入偏置或漏电流产生Rp上电压降

对于这种电流误差更加准确的描述应为"输入漏电流"。JFET 或 CMOS 放大器的漏电流量在 25°C 条件下低于 1 pA。这一规范与共模电压和幅度放大器功率无关。几乎所有的放大器都具有 ESD 单元,用于 ESD 事件保护,但是您在双极放大器中绝不会看到 ESD 漏电流。输入偏置电流超过 ESD 单元的几微安漏电流。

输入偏置和输入漏电流会随温度而变化。然而,根据不同的运算放大器设计,双极输入偏置电流可以非常稳定。但是,JFET 和 CMOS 输入放大器可能并非如此。由于漏电流来自反向偏置 ESD 二极管,因此温度每改变 10°C 漏电流便增加约 2 倍。

在确保输入漏电流保持与 JFET 和 CMOS 放大器一样低的过程中,您必须了解您的 PCB(印制电路板)对微微安级别电流的影响。例如,少量的灰尘、油或者水分子都会增加漏电流,并冒充输入偏置电流。但只要您特别小心,便可以构建一款符合 1-pA 性能规范的 PCB。

能够降低或者最小化输入偏置或输入漏电流的最有效方法是检查您的电路结构。您在检查电路时,请查看每个节点的电压特性,并确保您了解您的电路中所有电流通路的影响。

- 使用简化电路的高压放大器(11-21)

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 对数放大器的技术指标(11-26)

- 一种增大放大器增益的方法(11-28)

- 对数放大器的典型应用 (11-26)

- AGC中频放大器的设计 (11-29)