同步降压MOSFET电阻比的正确选择

在这篇《电源设计小贴士》中,我们将研究在同步降压功率级中如何对传导功耗进行折中处理,而其与占空比和 FET 电阻比有关。进行这种折中处理可得到一个用于 FET 选择的非常有用的起始点。通常,作为设计过程的一个组成部分,您会有一套包括了输入电压范围和期望输出电压的规范,并且需要选择一些 FET。另外,如果您是一名 IC 设计人员,则您还会有一定的预算,其规定了 FET 成本或者封装尺寸。这两种输入会帮助您选择总 MOSFET 芯片面积。之后,这些输入可用于对各个 FET 面积进行效率方面的优化。

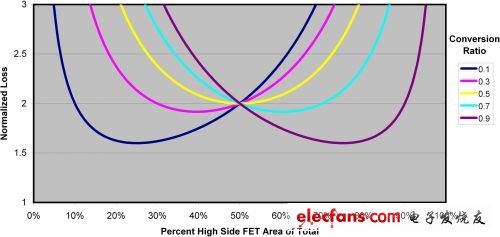

图 1 传导损耗与 FET 电阻比和占空比相关

首先,FET 电阻与其面积成反比例关系。因此,如果为 FET 分配一定的总面积,同时您让高侧面积更大(旨在降低其电阻),则低侧的面积必须减小,而其电阻增加。其次,高侧和低侧 FET 导电时间的百分比与VOUT/VIN 的转换比相关,其首先等于高侧占空比 (D)。高侧 FET 导通 D 百分比时间,而剩余 (1-D) 百分比时间由低侧 FET 导通。图 1 显示了标准化的传导损耗,其与专用于高侧 FET 的 FET 面积百分比(X 轴)以及转换因数(曲线)相关。很明显,某个设定转换比率条件下,可在高侧和低侧之间实现最佳芯片面积分配,这时总传导损耗最小。低转换比率条件下,请使用较小的高侧 FET。反之,高转换比率时,请在顶部使用更多的 FET。面积分配至关重要,因为如果输出增加至 3.6V,则针对 12V:1.2V 转换比率(10% 占空比)进行优化的电路,其传导损耗会增加 30%,而如果输出进一步增加至 6V,则传导损耗会增加近80%。最后,需要指出的是,50% 高侧面积分配时所有曲线都经过同一个点。这是因为两个 FET 电阻在这一点相等。

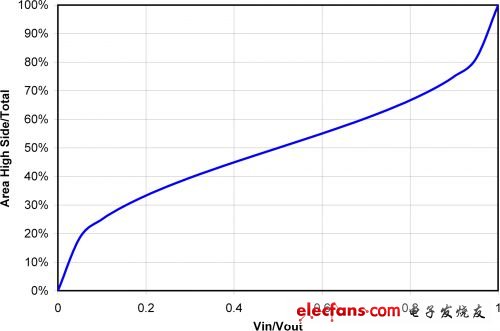

图 2 存在一个基于转换比率的最佳面积比

注意:电阻比与面积比成反比

通过图 1,我们知道 50% 转换比率时出现最佳传导损耗极值。但是,在其他转换比率条件下,可以将损耗降至这一水平以下。附录 1 给出了进行这种优化的数学计算方法,而图 2 显示了其计算结果。即使在极低的转换比率条件下,FET 芯片面积的很大一部分都应该用于高侧 FET。高转换比率时同样如此;应该有很大一部分面积用于低侧。这些结果是对这一问题的初步研究,其并未包括如高侧和低侧FET之间的各种具体电阻值,开关速度的影响,或者对这种芯片面积进行封装相关的成本和电阻等诸多方面。但是,它为确定 FET之间的电阻比提供了一个良好的开端,并且应会在FET选择方面实现更好的整体折中。

下次,我们将讨论如何确定 SEPIC 所用耦合电感的漏电感要求,敬请期待。本文及其他电源解决方案的更多详情,请访问:www.ti.com.cn/power。

附录:图 2 的推导过程

- 如何设计一个合适的系统电源(上)(11-20)

- 什么是MOSFET(11-26)

- 包含热模型的新型MOSFET PSPICE模型 (11-26)

- 用IGBT代替MOSFET的可行性分析(11-27)

- MOSFET的谐极驱动(11-27)

- 扩展升压稳压器输入、输出电压范围的级联 MOSFET (11-30)