现代高速比较器

·内部或外部滞后— 滞后是一种介乎低到高开关电压和高到低开关电压之间的设计预算中或需激活的差别。有些比较器具备可调节滞后水平的功能,方法是通过在指定的引脚上施加电压。

·上升及下降时间—一般是输出电压的10%至90%的时间,并且上升和下降缘的时间可以有差别,假如这情况出现,那将会导致输出的周期时间会相对于输入信号而改变。

·触发率—指在某一个频率下,比较器的输出可以跟随输入的状态来变化。

·消散—量度传播延迟变化的参数。

·抖动—可以是随机或事前决定,负责量度信号缘在时间上的不定性。

将运算放大器作为比较器使用

由于运算放大器一般都是双路/四路的配置,用户可以考虑将多出来的放大器做为比较器来用。如前所述,此时有不少地方需注意。首先,时间选择很关键。当把运算放大器用作比较器时,其本身的增益带宽乘积、群延迟和压摆率等参数很可能会因内部频率补偿和饱和效应而误产生变化。对于优化的单器件来说,这种应用不失为一种经济增值方案。可是,对于比较复杂和可能阻碍性能发挥的四路器件来说,这种方案不但所占的空间较多,而且需要花费更多时间测试和调试以确

保运算放大器的特性能够配合。运放用作比较器时需要注意以下几点:

·细阅数据表上叙述的运放拓扑和提示信息。

·注意源阻抗、共模输入范围和差分输入范围。

·放大器在过驱时的开关速度并计划为这参数进行大型扩展。

·注意温度变化带来的影响。

·通过检查负载阻抗、电源水平和电路的稳定性来确保输出已正确地连接到下一级。

·小心处理电路的设计和布局,例如即使只有很微量的输出通过分布电容和/或高输入阻抗被正反馈引入到输入端,都有可能引起振荡。

现代高速比较器

现今业界常用的比较器大多数是经过优化设计的,可为系统带来增值效益。最普遍的比较器应用类别是电平平移。现今,TTL和CMOS逻辑电平均已被广泛采用。对于高速应用而言,还可采用ECL(发射极耦合逻辑)、RSPECL(摆幅削减正发射极耦合逻辑)或LVDS(低压差分信号)。当需要从电缆和线路连接IC和FPGA,或在背板内的信号速度处于由每秒数百兆位至数千兆位的高速范围时,上述方案便会成为首选。LMH7220和 LMH7322便是可用作为高速/超高速电平比较变换的高速比较器件。

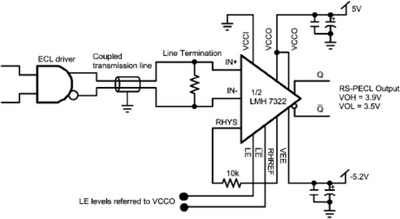

图2表示出一个LMH7322双高速比较器,并且以ECL变换到RSPECL的转换器方式实现。ECL高速逻辑已经沿用了很多年,尤其是供军事或测量用以及工业用的高档设置,而且它们属于负电压电平参考信号(-5.2V接地),难以连接到其它分离电源或单电源系统。幸而,LMH7322不单可有效解决上述的问题,与此同时比较起一般的逻辑电平移位器,它可提供给设计人员更大的自由度。该比较器在输入和输出电路上拥有不同的电源引脚,而其电源可以是由2.7V至12V的单一电源,又或是由±6V至±1.35V的分离电源。器件在输入时的共模范围可超出最低的电源电平200mV,从而令能在如此低的输入信号电平下感测到细微的信号。在高边上,共模范围受到1.5V的VCCI的限制,但需配合2.7V的VCCI和VCCO,还是有可能在输出上提供PECL逻辑电平。

图2 ECL 到 RSPECL 的电平变换

假如典型的上升和下降时间为160ps,而典型的传播延迟则为700ps,那便可促使该比较器为高速至每秒数千兆位的信号进行缓冲和电平平移,从而使电路适合应用在高速数据、时移、缓冲,或是来自电缆或背板的信号恢复。一个可调节的滞后可通过HYST引脚来施行,这做法对于失真信号或DC耦合线路或移动缓慢的信号来说最为受用,因为这可避免出现不必要的开关和触发。图2中的应用电路表示出输入VCCI信号是处于系统接地电平,而VCCO电平和VEE电平则分别处于+5V和-5.2V(这便是ECL驱动器负电源电平)。此外,输出电压将可符合RSPECL的规格。同一个器件可以用来介接到其他的逻辑电平,只需稍为调节VCCI和VCCO及VEE电压电平便可。加入例如是50W的适当线路端接是有可能的,图3所示为一基本端接例子。

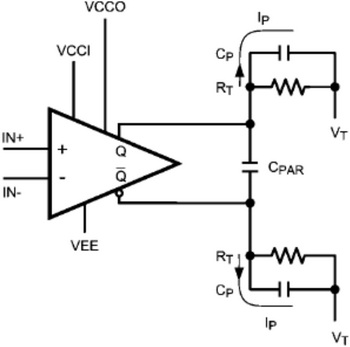

图3中的差分输出以一个跟随着电源电流的发射极来实现,并且确保两个输出引脚之间的摆幅差别有400mV。假如这里采用有源端接,那电压便会低于VCCO电平2V,否则每当端接到芯片的最负电源时,便需计算出正确的负载电阻。

图3 LMH7322的输出线路端接例子

此外,上升/下降时间或带有消散的传播延迟等参数均需要慎重考虑,而且它们不是全部都被规定。消散可以因共模、过驱和压摆率的变化而引致,从而影响传播延迟、工作周期和抖

- 建立比较器的外部滞回电压(11-28)

- 比较器的合理选择(06-09)

- 采用新型放大器实现高性能的电流检测(05-10)

- 适用于SAR ADC的CMOS比较器的设计(01-02)

- 利用低功耗比较器自动检测音频附件(05-11)

- 高性能CMOS集成电压比较器设计(10-07)