板级电路内建自测试建模技术研究

指标较低的一个原因就是可用信号数量少。这是受系统结构所限。对于板级系统,某些指标由于缺少检测设备而无法测试;有些指标由于缺少测试通道使得测试数据无法采集;有些指标由于与系统正常功能无关而被设计者忽略了。基于此,对数据采集器重新设计以增加可用信号,改善可测性。

①在FPGA 内设计可调节输入信号产生电路DSP 模块控制。

②截止频率测试电路,通过输入方波采集输出平均电压的方式,获取滤波器的截止频率。

③由DSP 控制专用边界扫描芯片完成具有边界扫描结构芯片的测试。主要实现FPGA 内核逻辑的测试。

④把FPGA 内的逻辑电路依据功能进行分块设计,原则就是要尽可能减少逻辑电路模块之间的信号联系,使模块电路的输入信号数目减少。

⑤FPGA 内部设计数据采集器获取锁相环输出频率。

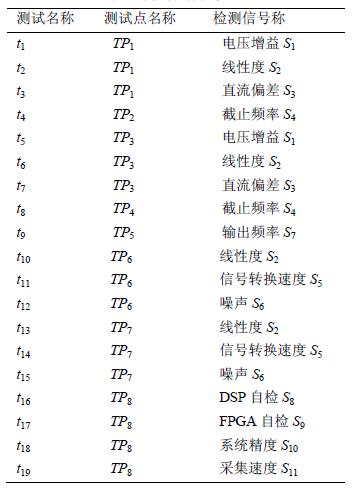

通过重新设计使得原数据采集器不能测试的参数都可以作为信号了。现在增加6 个信号:截止频率、转换速度、噪声、PLL 输出频率、DSP 自检指标和FPGA 自检指标。所以现在选取的信号有11 个,重新编号后显示如下。S1-增益、S2-线性度、S3-直流偏差、S4-截止频率,S5-转换速度,S6-转换噪声,S7- PLL 输出频率,S8-转换速度,S9- FPGA 自检指标,S10-系统精度,S11-采集速率。新的信号与元件依赖关系见表3。

表3 元件与信号关联关系

(3)新信号的加入使得系统必须增加新的测试点和新的测试项目。新的测试方案增加了4 个测试点,为检测所有信号使得测试增加到了19 个,对新模型重新进行可测性分析后发现有4 个冗余测试。所以新测试方案含有15 个测试项目。具体测试项目的名称、测试内容和测试位置见表4。

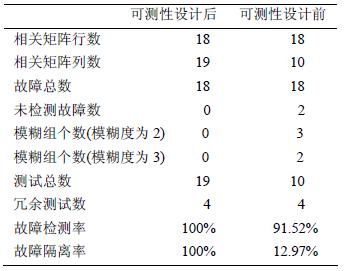

进可测性设计后,原来未检测故障已能检测到,故障检测率有原来的1.72% 提高到100% ;并且所有未隔离故障均以隔离到一个模块,使得所有故障全部区分开,即故障隔离率有设计前的12.97% 提高到100% 。可测性设计后的数据采集器的可测性分析结果与原数据采集的分析结果列于表5,由此表可以看出可测性提高效果。

4. 结论

本文通过建立高速数据采集器的多信号流模型,对数据采集器进行了可测性分析与可测性设计,通过可测性设计其故障检测率和故障隔离率均达到100% ,在此基础上可以通过DSP 完成整个电路的自测试。本文的研究成果为提高电路的自测试能力奠定基础,可适应现场快速故障诊断和故障定位的需要。本文作者创新点:提出了一种板级电路内建自测试建模技术,针对原有电子系统增加内建自测试的可测性技术,并采用多信号流作为评估方法,通过实际系统验证了所提出方法的可行性和实际价值。

表4 测试名称及位置

表5 可测性改善对比表

参考文献

[1] GJB2547-95 .装备测试性大纲[S].北京:国家科学技术工业委员会,1995

[2] 田仲,石君友.系统测试性设计分析与验证[M].北京:北京航空航天大学出版社,2003

[3] 康中尉.可测试性设计研究[J]《.微计算机信息》,2008,1-1:157-159

[4] SOMNATH Deb, KRISHHA R PatTIpati, VIJAY Raghavan, et al.Multi-signal flow graphs: a novel approach for system testability analysis and fault diagnosis.1994 IEEE Autotestcon Proceedings, 1994, 361-373

[5] Deb, S., Ghoshal, S., Malepati, V.N. and Kleinman, D.L., 2000, Tele-diagnosis: Remote monitoring of large-scale systems, Proceedings of the IEEE Aerospace Conference, Big Sky,MT

[6] 杨智勇,许爱强,牛双诚.基于多信号模型的系统测试性建模与分析[J].工程设计学报,2007,14(5):364-368,394

[7] Jianhui Luo, Haiying Tu, Krishna Pattipati, Liu Qiao and Shunsuke Chigusa, "Graphical models for diagnostic knowledge representation and inference," IEEE Instrument and Measurement Magazine, Vol. 9, No. 4, pp. 45 – 52, Aug., 2006

[8]Jianhui Luo, Kihoon Choi, Krishna R. Pattipati, Liu Qiao and Shunsuke Chigusa, "Distributed fault diagnosis for networked, embedded automotive and aerospace systems," Proc. Of IEEE International Conference on Systems, Man, and Cybernetics, Taipei, Taiwan, Oct., 2006

[9] F. Tu, K. R. Pattipati, S. Deb, and V. N. Malepati, "Computationally efficient algorithms for multiple fault diagnosis in large graph-based systems," IEEE Transactions on Systems, Man and Cybernetics–Part A, vol. 33, no. 12, pp. 73–85, 2003

[10]M. Shakeri, "Advances in system faultmodeling and diagnosis," Ph.D. dissertation, Univ. of Connecticut, Storrs, 1996

[11]G. Simon, G. Biswas, S. Abdelwahed, N. Mahadevan, T. Szemethy, G. Peceli, and T. Kovashazy, "Model-based fault-adaptive control of complex dynamic systems," in Proc. Instrumentation Measurement TechnologyConf., Vail, CO, May, 20–22 2003

- 板级电路多信号模型的自测试技术介绍(10-16)