有关交错ADC的更多观点

作者:Jonathan Harris

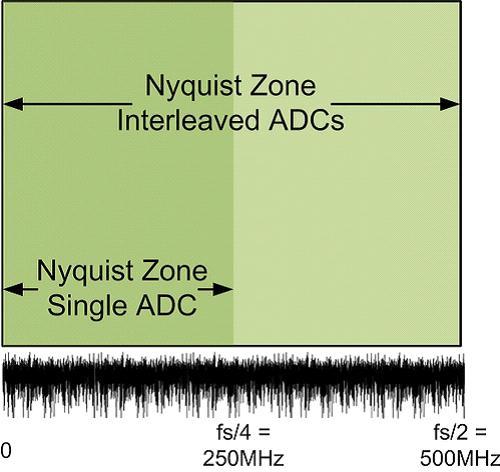

交错结构的优势可惠及多个细分市场。 最有用的优势是通过交错ADC更宽的奈奎斯特区增加带宽。 同样,我们首先举两个500MSPS ADC交错建立1000MSPS采样速率的例子。 通过交错两个ADC,可以大幅增加带宽。 注意,fS显示的是一个转换器;交错转换器采样速率等于2 X fS。

两个交错ADC – 奈奎斯特区

它可以为各种不同应用提供优势。 很多设计中的内在系统要求都超前于商用ADC技术。 无论ADC采样速率有多高,市场似乎都要求更高的速率。 交错结构可填补技术空白。 军事和航空应用正要求更高的带宽,以实现更佳的空间识别能力。 此外,在后端通信中也需要增加通道带宽。

就像蜂窝标准增加了通道带宽和工作频段数一样,对ADC可用带宽的要求也越来越高。 在某些市场和应用中,还出现了转移到直接RF采样的需求,这样无线电设计的级数更少,并可移除解调器。 ADC具有足够高的采样速率还有可能降低时钟要求。 因此,将ADC与DAC时钟对齐便是可行的,从而简化系统设计。 在仪器仪表和测量应用中,需要用到更高的带宽,以获取并测量信号。

更高的采样速率能为这些应用提供更多带宽。 它能使频率规划更轻松,并降低通常用于ADC输入端的抗混叠滤波器的复杂程度和成本。

有那么多的优势,您一定会问这些优势的代价是什么。 就像大部分事情一样,天下没有免费的午餐。 交错ADC具有更高的带宽和其他有用的优势,但同时也带来了一些挑战。

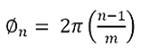

我们能组合使用多少转换器? 让我们简单看一下交错ADC的时钟要求:

m = 2时,此等式很容易求解。 然而,当m等于别的数(比如8)时,时钟要求变得非常复杂。将m代入,并求解8个转换器的等式,得到所需的时钟相位为:0、45、90、135、180、225、270和315度。 若输入时钟频率较低,那问题不大;但采用交错结构的重点就是获得高采样速率。

实际情况中,时钟频率为1GHz。 这意味着时钟电路必须要能划分输入时钟,并创建相距125ps的相位;同时,还必须精确完成此操作。 时钟的任何误差或抖动都会降低性能。